# iW-RainboW-G51M Intel Agilex 7 SoC FPGA (R24C) SOM Hardware Datasheet

### **Document Revision History**

| Document Number |                           | iW-PRHFZ-UM-01-R1.0-REL0.2-Hardware |

|-----------------|---------------------------|-------------------------------------|

| Release Date    |                           | Description                         |

| 0.1             | 13 <sup>th</sup> Feb 2024 | Draft Version                       |

| 0.2             | 14 <sup>th</sup> Feb 2024 | Updated Draft Version               |

PROPRIETARY NOTICE: This document contains proprietary material for the sole use of the intended recipient(s). Do not read this document if you are not the intended recipient. Any review, use, distribution or disclosure by others is strictly prohibited. If you are not the intended recipient (or authorized to receive for the recipient), you are hereby notified that any disclosure, copying distribution or use of any of the information contained within this document is STRICTLY PROHIBITED. Thank you. "iWave Systems Tech. Pvt. Ltd."

### Disclaimer

iWave Systems reserves the right to change details in this publication including but not limited to any Product specification without notice.

No warranty of accuracy is given concerning the contents of the information contained in this publication. To the extent permitted by law no liability (including liability to any person by reason of negligence) will be accepted by iWave Systems, its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document.

CPU and other major components used in this product may have several silicon errata associated with it. Under no circumstances, iWave Systems shall be liable for the silicon errata and associated issues.

### **Trademarks**

All registered trademarks, product names mentioned in this publication are the property of their respective owners and used for identification purposes only.

### Certification

iWave Systems Technologies Pvt. Ltd. is an ISO 9001:2015 Certified Company.

# TEV NORD XV inth Thinks IS. \$50 900

### **Warranty & RMA**

Warranty support for Hardware: 1 Year from iWave or iWave's EMS partner.

For warranty terms, go through the below web link,

http://www.iwavesystems.com/support/warranty.html

For Return Merchandise Authorization (RMA), go through the below web link,

http://www.iwavesystems.com/support/rma.html

### **Technical Support**

iWave Systems technical support team is committed to provide the best possible support for our customers so that our Hardware and Software can be easily migrated and used.

For assistance, contact our Technical Support team at,

Email : <u>support.ip@iwavesystems.com</u>

Website : <u>www.iwavesystems.com</u>

Address : iWave Systems Technologies Pvt. Ltd.

# 7/B, 29<sup>th</sup> Main, BTM Layout 2<sup>nd</sup> Stage,

Bengaluru, Karnataka,

India - 560076

### **Table of Contents**

| 1. | INTRO | DDUCTION                                                     | 7    |

|----|-------|--------------------------------------------------------------|------|

| 1. | .1 P  | Purpose                                                      | 7    |

| 1. | .2 S  | OM Overview                                                  | 7    |

| 1  | .3 L  | ist of Acronyms                                              | 7    |

| 1  | .4 T  | erminlogy Description                                        | 9    |

| 1  | .5 R  | References                                                   | 9    |

| 2. | ARCH  | ITECTURE AND DESIGN                                          | . 10 |

| 2  | .1 lı | ntel Agilex 7 SoC FPGA (R24C) SOM Block Diagram              | .10  |

| 2  | .2 lı | ntel Agilex 7 SoC FPGA SOM Features                          | .11  |

| 2  | .3 lı | ntel Agilex 7 SoC FPGA (R24C)                                | .13  |

|    | 2.3.1 | Intel Agilex 7 Power                                         | .15  |

|    | 2.3.2 | Intel Agilex 7 Reset                                         | .15  |

|    | 2.3.3 | Intel Agilex 7 Reference Clock                               | .15  |

|    | 2.3.4 | Intel Agilex 7 SoC and FPGA Configuration & Status           | .17  |

|    | 2.3.5 | Intel Agilex 7 Boot Mode Switch                              | .17  |

|    | 2.3.6 | Agilex 7 SoC/FPGA High Speed Transceivers                    | .18  |

| 2  | .4 N  | Летогу                                                       | .19  |

|    | 2.4.1 | DDR4 SDRAM with ECC for HPS                                  | .19  |

|    | 2.4.2 | DDR4 SDRAM1 for FPGA                                         | .19  |

|    | 2.4.3 | Dual QDR-IV for FPGA                                         | .19  |

|    | 2.4.4 | eMMC Flash                                                   | .20  |

|    | 2.4.5 | QSPI Flash                                                   | .20  |

| 2  | .5 C  | On SOM Features                                              | .21  |

|    | 2.5.1 | JTAG/ Active Serial Header                                   | .21  |

|    | 2.5.2 | Fan Header                                                   | .23  |

| 2  | .6 B  | Board to Board Connector1                                    | .24  |

|    | 2.6.1 | FPGA Interfaces                                              | .28  |

|    | 2.6.2 | FPGA High Speed Transceivers                                 | .28  |

|    | 2.6.3 | FPGA IOs & General-Purpose Clocks – Bank3A                   | .33  |

|    | 2.6.4 | HPS RGMII Interface                                          | .37  |

|    | 2.6.5 | Power Control Input                                          | .38  |

| 2  | .7 B  | Board to Board Connector2                                    | .39  |

|    | 2.7.1 | HPS & SDM Interfaces                                         | .43  |

|    | 2.7.  | .1.1 USB2.0 OTG Interface                                    | .43  |

|    | 2.7.  | .1.2 SD/SDIO Interface (Optional)                            | .44  |

|    | 2.7.  | .1.3 Debug UART Interface                                    | .45  |

|    | 2.7.  | .1.4 Data UART Interface                                     | .45  |

|    | 2.7.  | •                                                            |      |

|    | 2.7.  |                                                              |      |

|    |       | .1.7 Configuration QSPI Interface – From SDM Bank (Optional) |      |

|    | 2.7.2 | HPS to FPGA routed Interfaces.                               |      |

|    | 2.7.  | .2.1 Gigabit Ethernet Interface                              | .48  |

| 2.7.3 FPGA Interfaces         |                                | 49 |

|-------------------------------|--------------------------------|----|

| 2.7.3.1 High Speed Tran       | sceivers                       | 49 |

| 2.7.4 FPGA IOs & General-F    | Purpose Clocks – Bank2A        | 51 |

| 2.7.5 Power, Control & Res    | et Input                       | 56 |

| 2.8 Board to Board Connect    | or3                            | 57 |

| 2.8.1 FPGA Interfaces         |                                | 61 |

| 2.8.1.1 High Speed Tran       | sceivers                       | 61 |

| 2.8.2 Power, Control & Res    | et Input                       | 68 |

| 2.9 Intel Agilex 7 SoC and FF | PGA HPS Pin Multiplexing       | 69 |

| 3. TECHNICAL SPECIFICATION    |                                | 71 |

|                               |                                |    |

|                               | 5                              |    |

| 3.1.1 Power Input Requirer    | ment                           | 71 |

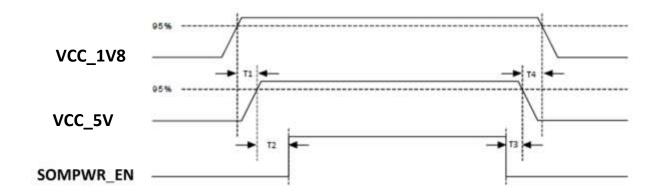

| 3.1.2 Power Input Sequenc     | ing                            | 72 |

| 3.1.3 Power Consumption       |                                | 73 |

| 3.2 Environmental Characte    | ristics                        | 74 |

| 3.2.1 Temperature Specific    | ation                          | 74 |

| 3.2.2 RoHS3 Compliance        |                                | 74 |

| 3.2.3 Electrostatic Discharg  | e                              | 74 |

| 3.2.4 Heat Sink               |                                | 75 |

| 3.3 MechanicalCharacterist    | ics                            | 76 |

| 3.3.1 Intel Agilex 7 SoC and  | FPGA SOM Mechanical Dimensions | 76 |

| 4. ORDERING INFORMATION       |                                | 77 |

|                               |                                |    |

| 5. APPENDIX                   |                                | 78 |

| 5.1 Intel Agilex 7 SoC and F  | PGA SOM Develonment Platform   | 78 |

# **List of Figures**

| Figure 1: Intel Agilex 7 SoC FPGA SOM Block Diagram                              | 10 |

|----------------------------------------------------------------------------------|----|

| Figure 2: Intel Agilex 7 SoC FPGA CPU Simplified Block Diagram                   | 13 |

| Figure 3: Intel Agilex 7 SoC FPGA F-Series Devices Comparison                    | 14 |

| Figure 4: JTAG/AS Header                                                         | 21 |

| Figure 5: Fan Header                                                             | 23 |

| Figure 6: Board-to-Board Connector1                                              | 24 |

| Figure 7: Board-to-Board Connector2                                              | 39 |

| Figure 8: Board-to-Board Connector3                                              | 57 |

| Figure 9: Power Input Sequencing                                                 | 72 |

| Figure 10: Mechanical dimension of Intel Agilex 7 SoC and FPGA SOM - Top View    | 76 |

| Figure 11: Mechanical dimension of Intel Agilex 7 SoC and FPGA SOM - Bottom View | 76 |

| Figure 12: Intel Agilex 7 SoC and FPGA SOM Development Platform                  | 78 |

|                                                                                  |    |

| List of Tables                                                                   |    |

| Table 1: Acronyms & Abbreviations                                                | 7  |

| Table 2: Terminology                                                             | 9  |

| Table 3: Intel Agilex 7 SoC and FPGA SOM Reference Clocks.                       | 15 |

| Table 4: JTAG & Active Serial Switch Truth Table                                 | 17 |

| Table 5: Configuration Selection Truth Table                                     | 18 |

| Table 6: Agilex 7 R24C SoC/FPGA Transceiver data rate performance                |    |

| Table 7: JTAG/Active Serial Header Pinout- JTAG is selected                      | 21 |

| Table 8: JTAG/Active Serial Header Pinout- Active Serial is selected             | 22 |

| Table 9: Fan Header Pinout                                                       | 23 |

| Table 10: Board to Board Connector1 Pinout                                       | 25 |

| Table 11: Board to Board Connector2 Pinout                                       | 40 |

| Table 12: Board to Board Connector3 Pinout                                       | 58 |

| Table 13: HPS IOMUX on Intel Agilex 7 SoC and FPGA SOM                           | 69 |

| Table 14: Power Input Requirement                                                | 71 |

| Table 15: Power Sequence Timing                                                  | 72 |

| Table 16: Power Consumption                                                      | 73 |

| Table 17: Temperature Specification                                              | 74 |

| Table 18: Orderable Product Part Numbers                                         | 77 |

### 1. INTRODUCTION

### 1.1 Purpose

This document is the Hardware User Guide for the Intel Agilex 7 SoC FPGA(R24C) System on Module. This board is fully supported by iWave Systems Technologies Pvt. Ltd. This Guide provides detailed information on the overall design and usage of the Intel Agilex 7 SoC FPGA System on Module from a Hardware Systems perspective.

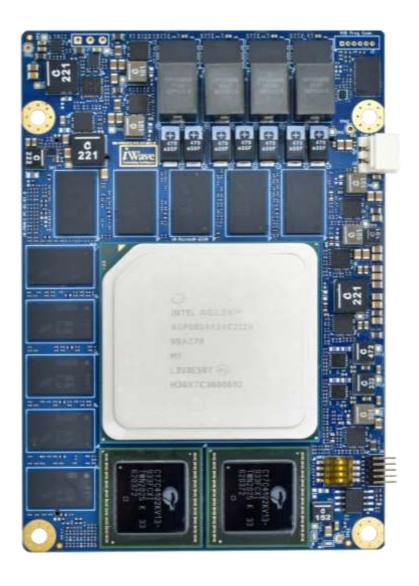

### 1.2 SOM Overview

The Intel Agilex 7 SoC FPGA (R24C) SOM is an extension of Intel Agilex 7 SoC FPGA(R24C). Intel Agilex 7 SoC FPGA (R24C) SOM has a form factor of 110mm x 75mm and provides the functional requirements for an embedded application. Two High-Speed High-Density ruggedized terminal strip connectors and One High-Speed High-Density connectors that facilitates the carrier board interfaces to carry all the I/O signals to and from the Intel Agilex 7 SoC FPGA SOM.

### 1.3 List of Acronyms

The following acronyms will be used throughout this document.

**Table 1: Acronyms & Abbreviations**

| Acronyms   | Abbreviations                                                               |

|------------|-----------------------------------------------------------------------------|

| ADC        | Analog to Digital Converter                                                 |

| ARM        | Advanced RISC Machine                                                       |

| BSP        | Board Support Package                                                       |

| CAN        | Controller Area Network                                                     |

| CPU        | Central Processing Unit                                                     |

| DDR4 SDRAM | Double Data Rate fourth-generation Synchronous Dynamic Random Access Memory |

| FPGA       | Field Programmable Gate Array                                               |

| еММС       | Embedded Multimedia Card                                                    |

| GB         | Giga Byte                                                                   |

| Gbps       | Gigabits per sec                                                            |

| GEM        | Gigabit Ethernet Controller                                                 |

| GHz        | Giga Hertz                                                                  |

| GPIO       | General Purpose Input Output                                                |

| I2C        | Inter-Integrated Circuit                                                    |

| IC         | Integrated Circuit                                                          |

| JTAG       | Joint Test Action Group                                                     |

| Kbps       | Kilobits per second                                                         |

| LVDS       | Low Voltage Differential Signalling                                         |

| MAC        | Media Access Controller                                                     |

| MB         | Mega Byte                                                                   |

| Mbps       | Megabits per sec                                                            |

| MHz        | Mega Hertz                                                                  |

| Acronyms | Abbreviations                               |

|----------|---------------------------------------------|

| NPTH     | Non-Plated Through hole                     |

| PCB      | Printed Circuit Board                       |

| PMIC     | Power Management Integrated Circuit         |

| PTH      | Plated Through hole                         |

| PL       | Programmable Logic                          |

| PS       | Processing System                           |

| RGMII    | Reduced Gigabit Media Independent Interface |

| RTC      | Real Time Clock                             |

| SD       | Secure Digital                              |

| SDIO     | Secure Digital Input Output                 |

| SGMII    | Serial Gigabit Media Independent Interface  |

| SoC      | System On Chip                              |

| SOM      | System On Module                            |

| SPI      | Serial Peripheral Interface                 |

| UART     | Universal Asynchronous Receiver/Transmitter |

| ULPI     | UTMI+ Low Pin Interface                     |

| USB      | Universal Serial Bus                        |

| USB OTG  | USB On the Go                               |

| UTMI     | USB2.0 Transceiver Macrocell Interface      |

### 1.4 Terminlogy Description

In this document, wherever Signal Type is mentioned, below terminology is used.

**Table 2: Terminology**

| Terminology | Description                                                          |  |  |  |  |

|-------------|----------------------------------------------------------------------|--|--|--|--|

| 1           | Input Signal                                                         |  |  |  |  |

| 0           | Output Signal                                                        |  |  |  |  |

| Ю           | Bidirectional Input/output Signal                                    |  |  |  |  |

| CMOS        | Complementary Metal Oxide Semiconductor Signal                       |  |  |  |  |

| LVDS        | Low Voltage Differential Signal                                      |  |  |  |  |

| GBE         | Gigabit Ethernet Media Dependent Interface differential pair signals |  |  |  |  |

| USB         | Universal Serial Bus differential pair signals                       |  |  |  |  |

| OD          | Open Drain Signal                                                    |  |  |  |  |

| OC          | Open Collector Signal                                                |  |  |  |  |

| Power       | Power Pin                                                            |  |  |  |  |

| PU          | Pull Up                                                              |  |  |  |  |

| PD          | Pull Down                                                            |  |  |  |  |

| NA          | Not Applicable                                                       |  |  |  |  |

| NC          | Not Connected                                                        |  |  |  |  |

Note: Signal Type does not include internal pull-ups or pull-downs implemented by the chip vendors and only includes the pull-ups or pull-downs implemented On-SOM.

### 1.5 References

- Agilex 7 Hard Processor Systems Technical Reference Manual

- Intel Agilex 7 Device Data Sheet

- Intel Agilex 7 Device Design Guidelines

### 2. ARCHITECTURE AND DESIGN

This section provides detailed information about the Intel Agilex 7 SoC FPGA (R24C) SOM features and Hardware architecture with high level block diagram. Also, this section provides detailed information about Board-to-Board connectors pin assignment and usage.

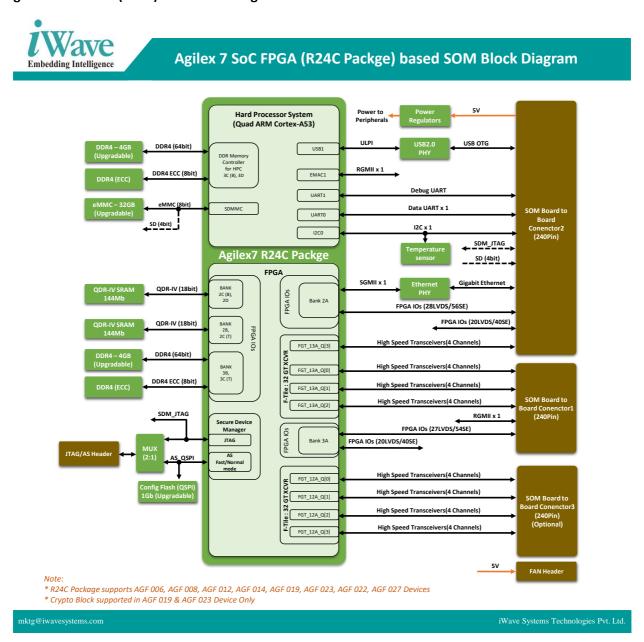

### 2.1 Intel Agilex 7 SoC FPGA (R24C) SOM Block Diagram

Figure 1: Intel Agilex 7 SoC FPGA SOM Block Diagram

### 2.2 Intel Agilex 7 SoC FPGA SOM Features

The Intel Agilex 7 SoC FPGA (R24C) SOM supports the following features.

### SoC

- The Intel Agilex 7 SoC FPGA

- Compatible Agilex 7 F-Series Agilex 7 AGF 006, AGF 008, AGF 012, AGF 014, AGF 019, AGF 022, AGF 023, AGF 027

- Hard Processing System (HPS)

- Quad-core 64-bit Arm Cortex-A53 up to 1.50 GHz

- Field Programmable Gate Array (FPGA)

- Up to 2,692,760 Logic elements

- 32 x FGT transceivers up to 32Gbps in NRZ or 58Gbps in PAM4 Format

### **Power**

Discrete Power Regulators

### Memory

- o 8GB DDR4 SDRAM (64bit + 8bit) with ECC for HPS (Expandable)<sup>1</sup>

- o 8GB DDR4 SDRAM (64bit + 8bit) with ECC for FPGA (Expandable)<sup>1</sup>

- o 2 x 144Mb QDR-IV (18bit) for FPGA

- o 1Gb QSPI Flash (Expandable)<sup>1</sup>

- 32GB eMMC Flash (Expandable)<sup>1</sup>

- o 4Kb EEPROM

### **Other On-SOM Features**

- Gigabit Ethernet PHY Transceiver<sup>2</sup>

- USB2.0 Transceiver

- Clock Synchronizer

- Temperature sensor

- o JTAG/Active Serial Header

- o Fan Header

### Board to Board Connector1 Interfaces (240pin)

### From FPGA Block

- o 12 x FGT transceivers up to 58Gbps<sup>3</sup>

- o 27 LVDS/54SE FPGA IOs from Bank 3A

### From HPS Block

1 x RGMII Interface

### **Board to Board Connector2 Interfaces (240pin)**

### From HPS Block

- O USB2.0 OTG x 1 Port (through On-SOM USB2.0 transceiver)

- SD (4bit) x 1 Port (Optional)

- o Debug UART x 1 Port

- Data UART x 1 Port (With CTS and RTS)

- o I2C x 1 Ports

### From SDM Block

- JTAG x 1

- AS x 1 (Active Serial x4)

### From HPS to FPGA Block

o Gigabit Ethernet x 1 Port (through On-SOM Gigabit Ethernet PHY transceiver) <sup>2</sup>

### From FPGA Block

- 4 x FGT transceivers up to 58Gbps

- 20 LVDS/40SE FPGA IOs from Bank 3A

- 28 LVDS/56SE FPGA IOs from Bank 2A

### **Board to Board Connector3 Interfaces (240pin)**

### From FPGA Block

16 x FGT transceivers up to 58Gbps<sup>3</sup>

### **General Specification**

Power Supply : 5V (from Board-to-Board Connector2)

o Form Factor: 110mm x 75mm.

<sup>&</sup>lt;sup>1</sup> The Expansion of DDR4, QSPI Flash and eMMC size/capacity are subject to availability of chips in market.

<sup>&</sup>lt;sup>2</sup> These interfaces are routed from HPS to FPGA.

<sup>&</sup>lt;sup>3</sup> F-Tile: Quad0 transceivers from all FGT banks do not support PAM4 speed; they only support NRZ 32Gbps.

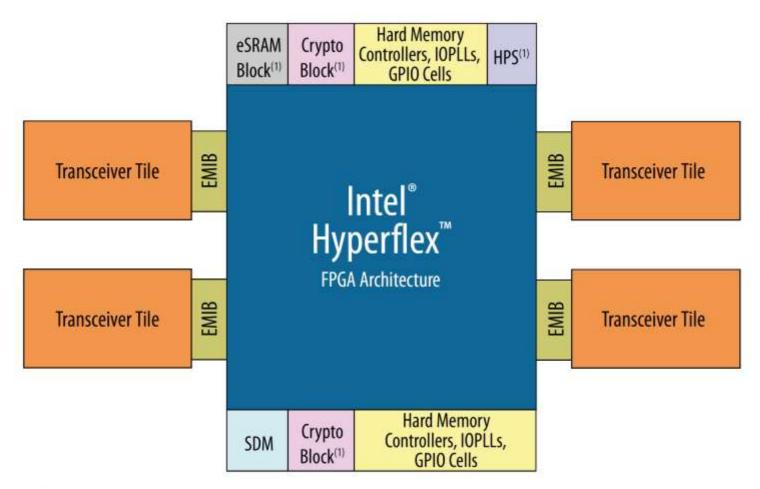

### 2.3 Intel Agilex 7 SoC FPGA (R24C)

Intel Agilex 7 FPGAs and SoCs are built using an innovative chiplet architecture, which provides agile and flexible integration of heterogeneous technology elements in a System-in-Package (SiP). The chiplet architecture enables Intel to address a broad array of acceleration and high-bandwidth applications with tailored and flexible solutions. Leveraging advanced 3D packaging technology such as Intel Embedded Multi-Die Interconnect Bridge (EMIB), the chiplet approach allows the combination of traditional FPGA die with purpose-built semiconductor die to create devices that are uniquely optimized for target applications.

The Intel® Agilex 7<sup>™</sup> F- and I-Series 10-nm SuperFin technology FPGAs and SoCs deliver on average 50% higher core performance or up to 40% lower power over previous generation high-performance FPGAs. These Intel® Agilex 7<sup>™</sup> FPGAs and SoCs accelerate system engineers' delivery of today's and tomorrow's most advanced high-bandwidth applications through ground-breaking features.

<sup>(1)</sup> Not available in all Intel Agilex devices. Refer to product tables for details.

Figure 2: Intel Agilex 7 SoC FPGA CPU Simplified Block Diagram

Note: Please refer the latest Intel Agilex 7 SoC FPGA Datasheet from Intel website for more details which may be revised from time to time.

The Intel Agilex 7 SoC FPGA SOM is compatible to R24C Package AGF 006, AGF 008, AGF 012, AGF 014, AGF 019, AGF 022, AGF 023, AGF 027.

| Produ                                 | ct Line                                                                              | AGF 006                                                                                                                                                                                                                                                                                                                                                                                                                    | AGF 008               | AGF 012              | AGF 014                 | AGF 019   | AGF 023   | AGF 022                                          | AGF 027     |  |

|---------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|-------------------------|-----------|-----------|--------------------------------------------------|-------------|--|

|                                       | Logic elements (LEs)                                                                 | 573,480                                                                                                                                                                                                                                                                                                                                                                                                                    | 764,640               | 1,178,525            | 1,437,240               | 1,918,975 | 2,308,080 | 2,208,075                                        | 2,692,760   |  |

|                                       | Adaptive logic modules (ALMs)                                                        | 194,400                                                                                                                                                                                                                                                                                                                                                                                                                    | 259,200               | 399,500              | 487,200                 | 650,500   | 782,400   | 748,500                                          | 912,800     |  |

|                                       | ALM registers                                                                        | 777,600                                                                                                                                                                                                                                                                                                                                                                                                                    | 1,036,800             | 1,598,000            | 1,948,800               | 2,602,000 | 3,129,600 | 2,994,000                                        | 3,651,200   |  |

|                                       | High-performance crypto blocks                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                     | 0                    | 0                       | 2         | 2         | 0                                                | 0           |  |

|                                       | eSRAM memory blocks                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                     | 2                    | 2                       | 1         | 1         | 0                                                | 0           |  |

|                                       | eSRAM memory size (Mb)                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                     | 36                   | 36                      | 18        | 18        | 0                                                | 0           |  |

|                                       | M20K memory blocks                                                                   | 2,844                                                                                                                                                                                                                                                                                                                                                                                                                      | 3,792                 | 5,900                | 7,110                   | 8,500     | 10,464    | 10,900                                           | 13,272      |  |

| Se                                    | M20K memory size (Mb)                                                                | 56                                                                                                                                                                                                                                                                                                                                                                                                                         | 74                    | 115                  | 139                     | 166       | 204       | 212                                              | 259         |  |

| ĕ                                     | MLAB memory count                                                                    | 9,720                                                                                                                                                                                                                                                                                                                                                                                                                      | 12,960                | 19,975               | 24,360                  | 32,525    | 39,120    | 37,425                                           | 45,640      |  |

| Şes                                   | MLAB memory size (Mb)                                                                | 6                                                                                                                                                                                                                                                                                                                                                                                                                          | 8                     | 12                   | 15                      | 20        | 24        | 23                                               | 28          |  |

|                                       | Fabric PLL                                                                           | 6                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                     | 8                    | 8                       | 5         | 5         | 12                                               | 12          |  |

|                                       | I/O PLL                                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                         | 12                    | 16                   | 16                      | 10        | 10        | 16                                               | 16          |  |

|                                       | Variable-precision digital signal processing (DSP) blocks                            | 1,640                                                                                                                                                                                                                                                                                                                                                                                                                      | 2,296                 | 3,743                | 4,510                   | 1,354     | 1,640     | 6,250                                            | 8,528       |  |

|                                       | 18 x 19 multipliers                                                                  | 3,280                                                                                                                                                                                                                                                                                                                                                                                                                      | 4,592                 | 7,486                | 9,020                   | 2,708     | 3,280     | 12,500                                           | 17,056      |  |

|                                       | Single-precison or half-precision tera floating point operations per second (TFLOPS) | 2.5 / 5.0                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.5 / 6.9             | 6.0 / 12.0           | 6.8 / 13.6              | 2.0 / 4.0 | 2.5 / 5.0 | 9.4 / 18.8                                       | 12.8 / 25.6 |  |

|                                       | Maximum EMIF x72²                                                                    | 4                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                     | 4                    | 4                       | 3         | 3         | 4                                                | 4           |  |

|                                       | Maximum differential (RX or TX) pairs                                                | 192                                                                                                                                                                                                                                                                                                                                                                                                                        | 288                   | 384                  | 384                     | 240       | 240       | 384                                              | 384         |  |

| es ge                                 | Maximum AIB interfaces                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                     | 2                    | 2                       | 4         | 4         | 4                                                | 4           |  |

| alla<br>E                             | Memory devices supported                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |                      | DDR4 and                | d QDR IV  |           |                                                  |             |  |

| Maximum Available<br>Device Resources | Secure device manager (SDM)                                                          | Provides SHA-384 bitstream integrity, ECDSA 256/384 bitstream authentication, AES-256 bitstream encryption, physically unclonable function (PUF) protected key storage, side-channel attack resistance, SPDM attestation, cryptographic services, physical anti-tamper support                                                                                                                                             |                       |                      |                         |           |           |                                                  |             |  |

| Maxim<br>Devic                        | Hard processor system                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                            | ache coherency unit,  |                      |                         |           |           | cess (DMA), system m<br>e (SPI) x4, I2C x5, gene |             |  |

| Sec                                   | F-Tile                                                                               | PCI Express* (PCIe*) hard IP block (Gen4 x16 ) or Bifurcateable 2x PCIe Gen4 x8 (EP) or 4x Gen4 x4 (RP) Transceiver channel count: 16 channels at 32 Gbps (NRZ) /12 channels at 58 Gbps (PAM4) - RS & KP FEC Advanced networking support: - Bifurcatable 400 GbE hard IP block (10/25/50/100/200/400 GbE FEC/PCS/MAC) - Bifurcatable 200 GbE hard IP block (10/25/50/100/200 Gbps FEC/PCS) IEEE 1588 V2 support PMA direct |                       |                      |                         |           |           |                                                  |             |  |

| Tile Resources                        | E-Tile                                                                               | Transceiver channel count: Up to 24 channels at 28.9 Gbps (NRZ) / 12 channels at 57.8 Gbps (PAM4) - RS & KP FEC¹ Networking support: - 400GbE (4 x 100GbE hard IP blocks (10/25 GbE FEC/PCS/MAC)) IEEE 1588 v2 support PMA direct                                                                                                                                                                                          |                       |                      |                         |           |           |                                                  |             |  |

|                                       | P-Tile                                                                               | PCIe hard IP block (I<br>SR-IOV 8PF / 2kVF<br>VirtlO support<br>Scalable IOV                                                                                                                                                                                                                                                                                                                                               | Gen4 x16) or Bifurcat | eable 2x PCIe Gen4 x | B (EP) or 4x Gen4 x4 (I | RP)       |           |                                                  |             |  |

Figure 3: Intel Agilex 7 SoC FPGA F-Series Devices Comparison

### 2.3.1 Intel Agilex 7 Power

The Intel Agilex 7 SoC FPGA SOM uses discrete power regulators Power Management. In Intel Agilex 7 SoC FPGA SOM, Core power, Periphery circuitry power (VCC and VCCP) is connected to a SmartVID regulator, where the voltage can be varied between 0.70V – 0.90V based on Temperature & Performance. The HPS I/O voltage (VCCIO\_HPS) is fixed to 1.8V. The I/O voltage details of each FPGA Bank & High-speed transceiver will be mentioned in the corresponding sections.

### 2.3.2 Intel Agilex 7 Reset

The Intel Agilex 7 SOM POR is taken care internally by SDM Block in device. Also, it supports warm reset input from Board-to-Board Connector2 pin 35 and connected to pin CA43, HPS\_COLD\_nRESET pin of the SDM Bank of the device.

### 2.3.3 Intel Agilex 7 Reference Clock

The Intel Agilex 7 SoC FPGA SOM supports on board clock generator for reference clock to different blocks of Intel Agilex 7 SoC and FPGA and to other On SOM peripherals. These reference clock details are mentioned in the below table.

Table 3: Intel Agilex 7 SoC and FPGA SOM Reference Clocks.

| Part Nu                | Clock                 | - 1 1  |                   | Drive Level |        | Termina<br>tion |      |

|------------------------|-----------------------|--------|-------------------|-------------|--------|-----------------|------|

| Source                 | Destination           | Type   | Source            | Destination | Source | Destinat<br>ion | tion |

| Si5341B-D-GM<br>OUT-0  | FPGA DDR2<br>REFCLK   | LVDS   | 100Hz-<br>250MHz  | 300MHz      | -      | -               | 100Ω |

| Si5341B-D-GM<br>OUT-1  | FPGA<br>REFCLK        | LVDS   | 100Hz-<br>1028MHz | 100MHz      | -      | -               | -    |

| Si5341B-D-GM<br>OUT-2  | FPGA DDR1<br>REFCLK   | LVDS   | 100Hz-<br>1028MHz | 300MHz      | -      | -               | 100Ω |

| Si5341B-D-GM<br>OUT-3p | HPS<br>OSC Clock      | LVCMOS | 100Hz-<br>1028MHz | 25MHz       | -      | -               | 33Ω  |

| Si5341B-D-GM<br>OUT-3n | Ethernet PHY<br>Clock | LVCMOS | 100Hz-<br>1028MHz | 25MHz       |        |                 | 33Ω  |

| Si5341B-D-GM<br>OUT-4p | SDM<br>OSC Clock      | LVCMOS | 100Hz-<br>250MHz  | 125MHz      | -      | -               | 33Ω  |

| Si5341B-D-GM<br>OUT-5  | FGT_13A_Q2<br>REFCLK  | LVDS   | 100Hz-<br>250MHz  | 156.25MHz   | -      | -               | -    |

| Si5341B-D-GM<br>OUT-6p | USB TR<br>REFCLK      | LVCMOS | 100Hz-<br>250MHz  | 24MHz       | -      | -               | 33Ω  |

| Si5341B-D-GM<br>OUT-7  | FGT_12A_Q2<br>REFCLK  | LVDS   | 100Hz-<br>250MHz  | 156.25MHz   | -      | -               | -    |

| Si5341B-D-GM<br>OUT-8  | FPGA QDR1<br>REFCLK   | LVDS   | 100Hz-<br>1028MHz | 266.6MHz    | -      | -               | 100Ω |

| Part Nu               | Clock               | Frequency |                   | Drive Level |        | Termina<br>tion |      |

|-----------------------|---------------------|-----------|-------------------|-------------|--------|-----------------|------|

| Source                | Destination         | Type      | Source            | Destination | Source | Destinat<br>ion | tion |

| Si5341B-D-GM<br>OUT-9 | FPGA QDR2<br>REFCLK | LVDS      | 100Hz-<br>1028MHz | 266.6MHz    | -      | -               | 100Ω |

### Note:

<sup>&</sup>lt;sup>1</sup> Si5341B-GM: Drive strength is register programmable setting and stored in NVM.

<sup>\*</sup> Optional

### 2.3.4 Intel Agilex 7 SoC and FPGA Configuration & Status

The Intel Agilex 7 SoC and FPGA uses multi-stage boot process that supports both a non-secure and a secure boot. It supports different configuration schemes -JTAG-based configuration, AS Fast or Standard POR configuration. These configuration schemes are selected using the MSEL pin setting.

The SDM is the master of the boot and configuration process. Upon reset, device executes code out of on-chip ROM and copies the First stage boot loader (FSBL) from the boot device to the on-chip RAM. The FSBL initiates the boot of the HPS first and then configure the FPGA or it can be set to configure the FPGA first, then boot the HPS.

The Intel Agilex 7 SoC and FPGA SOM supports LED for the FPGA Configuration status indication namely CONFIG\_DONE. LED interfaced to CONFIG\_DONE and it is asserted when the FPGA configuration is complete. It is used to indicate if the FPGA is configured or not.

### 2.3.5 Intel Agilex 7 Boot Mode Switch

The Intel Agilex 7 SoC and FPGA always boots from SDM first and then boots the HPS or FPGA. Intel Agilex 7 SoC and FPGA supports the SDM QSPI or JTAG as the First Stage Bootloader in Standard or Fast Mode. Upon device reset, Intel Agilex 7 SoC and FPGA MSEL pins are read to determine the primary boot device. The ON SOM Switch also supports to switch between Active serial or JTAG connectivity on the On SOM Header. Also Direct to Factory Image option is made available on the switch.

The Intel Agilex 7 SoC and FPGA SOM supports Switching between Active Serial & JTAG Connectivity on the On SOM Header using the POS3 of the switch. Refer the below table to select between JTAG & Active Serial.

**Table 4: JTAG & Active Serial Switch Truth Table**

| Intel Agilex 7 -AS/JTAG                   | SW 1 (4 Position Switch-POS3) |                       |  |  |

|-------------------------------------------|-------------------------------|-----------------------|--|--|

| Header selection                          | POS 3                         | Switch Position Image |  |  |

| SDM JTAG<br>on<br>AS/JTAG Header          | OFF                           | 1 2 3 4               |  |  |

| SDM Active Serial<br>on<br>AS/JTAG Header | ON                            | 1 2 3 4               |  |  |

The Intel Agilex 7 SoC and FPGA SOM supports selection between the different configuration schemes making use of POS1 and POS2 the switch. Refer the below table to select between the different configuration schemes.

**Table 5: Configuration Selection Truth Table**

| Intel Agilex 7                   | SW (4 Position Switch-POS1 &POS2) |       |                         |  |  |  |

|----------------------------------|-----------------------------------|-------|-------------------------|--|--|--|

| Configuration Scheme             | POS 1                             | POS 2 | Curitale Desition Image |  |  |  |

| Selection                        | MSEL2                             | MSEL1 | Switch Position Image   |  |  |  |

| Active Serial -<br>Fast Mode     | OFF                               | OFF   | ON 74                   |  |  |  |

| Active Serial -<br>Standard Mode | OFF                               | ON    | ON 74                   |  |  |  |

| JTAG Only Mode                   | ON                                | ON    | ON 1C                   |  |  |  |

### 2.3.6 Agilex 7 SoC/FPGA High Speed Transceivers

The Agilex 7 SoC/FPGA SOM supports 24 high speed transceivers on Board-to-Board connectors from Agilex 7 FPGA fabric. The Agilex 7 SoC/FPGA has two high speed transceiver banks (12A & 13A) and each transceiver bank has four quad and each quad supports four high speed transmit and receive channels. So, total 16 high speed transmit and receive channels for each bank. Also, each high-speed transceiver quad supports two reference clock input pairs and last two quad supports each one reference clock output pairs. Transceiver data rate performance is based on the transceiver speed grade of the Agilex 7 SoC/FPGA as mentioned in the below table.

Table 6: Agilex 7 R24C SoC/FPGA Transceiver data rate performance

| Description         | Condition | Trans     | Unit      |        |       |

|---------------------|-----------|-----------|-----------|--------|-------|

| Description         |           | -1        | -2        | -3     | Offic |

| Supported data rate | NRZ       | 1–32.45   | 1–32      | 1–17.4 | Gbps  |

|                     | PAM4      | 20–58.125 | 20–58.125 | 20–32  | Gbps  |

Note: FGT Quad0 can only support 20-32 Gbps PAM4. FGT Quad1, Quad2, and Quad3 can support 20-58 Gbps PAM4.

The Agilex 7 SoC/FPGA SOM supports 12 high speed transceiver channels from Bank 13A Quad0, Quad1 & Quad2 along with two reference clock input pairs of each quad on Board to Board connector1 and 16 high speed transceiver channels from Bank 12A Quad0, Quad1, Quad2, Quad3 along with two reference clock input pairs of each quad on Board-to-Board conenctor3 and 4 high speed transceiver channels from Bank 13A Quad3 along with two reference clock input pairs of quad on Board-to-Board conenctor1. In Agilex 7 SoC/FPGA SOM, on board termination and AC coupling capacitors are not supported on transceiver lines. So it has to be taken care in the carrier board if required.

### 2.4 Memory

### 2.4.1 DDR4 SDRAM with ECC for HPS

The Intel Agilex 7 SoC and FPGA SOM supports 64bit, 8GB DDR4 RAM memory for Intel Agilex 7 HPS. Four 16 bit, 2GB DDR4 SDRAM ICs are used to support total on board HPS RAM memory of 8GB. Also, Intel Agilex 7 SoC and FPGA SOM supports 8bit ECC for RAM memory. These DDR4 devices operates at 1600MHz in -1 Speed Grade devices and 1334Mhz and 1200MHz speed respectively in -2 and -3 Speed Grade Devices. DDR4 memory is connected to the hard memory controller supported Banks- 3C and 3D. The RAM size can be expandable based on the availability of higher density 16bit DDR4 device.

The HPS DDR4 reference clock is connected to Bank 3D -G5 & F6 pins through on SOM clock synthesizer.

Note: Refer **ORDERING INFORMATION** section for exact RAM size used on the SOM based on the Product Part Number.

### 2.4.2 DDR4 SDRAM1 for FPGA

The Intel Agilex 7 SoC and FPGA SOM supports 2 x 64bit, 8GB DDR4 RAM memory for Intel Agilex 7 FPGA. For the first FPGA DDR4 SDRAM, four 16 bit, 2GB DDR4 SDRAM ICs are used to support a total on board FPGA RAM memory of 8GB. Also, Intel Agilex 7 SoC and FPGA SOM supports 8bit ECC for RAM memory. These DDR4 devices operates at 1600MHz in -1 Speed Grade devices and 1334Mhz and 1200MHz speed respectively in -2 and -3 Speed Grade Devices. DDR4 memory is connected to the FPGA Banks- 2C and 2D. The RAM size can be expandable based on the availability of higher density 16bit DDR4 device.

The FPGA1 DDR4 reference clock is connected to Bank 2C -DE36 & DD35 pins through on SOM clock synthesizer.

Note: Refer **ORDERING INFORMATION** section for exact RAM size used on the SOM based on the Product Part Number.

### 2.4.3 Dual QDR-IV for FPGA

The Intel Agilex 7 SoC and FPGA SOM supports dual 18bit, 144Mb QDR-IV RAM memory for Intel Agilex 7 FPGA. These QDR-IV devices operate at 1066MHz in -1 & -2 Speed Grade devices and 933MHz speed respectively in -3 Speed Grade Devices. 1st QDR-IV memory is connected to the FPGA Banks- 2C and 2D and 2nd QDR-IV connected to the FPGA Banks- 2B and 2C Bank.

The 1st QDR-IV reference clock is connected to Bank 2D -DD12 & DC13 pins through on SOM clock synthesizer.

The 2<sup>nd</sup> QDR-IV reference clock is connected to Bank 2B -DD36 & DC37 pins through on SOM clock synthesizer.

Note: Refer **ORDERING INFORMATION** section for exact RAM size used on the SOM based on the Product Part Number.

### 2.4.4 eMMC Flash

The Intel Agilex 7 SoC and FPGA SOM supports 32GB eMMC Flash memory for Second Stage Boot & Storage of Intel Agilex 7 SoC and FPGA. This eMMC Flash memory is directly connected to the SDMMC controller in HPS Block of the Intel Agilex 7 SoC and FPGA and operates at 1.8V Voltage level. This SD/SDIO controller supports eMMC5.0 standard with up to 8bit HS200 mode. The eMMC Flash size can be expandable based on the availability of higher density eMMC Flash device.

Note: Refer ORDERING INFORMATION section for exact eMMC Flash size used on the SOM based on the Product Part Number.

### 2.4.5 QSPI Flash

The Intel Agilex 7 SoC and FPGA SOM supports 1Gb QSPI Flash memory for First Stage Boot & Storage of Intel Agilex 7 SoC and FPGA. This QSPI Flash memory is directly connected to the SDM controller of the Intel Agilex 7 SoC and FPGA SDM and operates at 1.8V Voltage level. The QSPI Flash size can be expandable based on the availability of higher density chips.

Note: Refer **ORDERING INFORMATION** section for exact QSPI Flash size used on the SOM based on the Product Part Number.

### 2.5 On SOM Features

### 2.5.1 JTAG/ Active Serial Header

The Intel Agilex 7 SoC and FPGA SOM supports 10Pin JTAG/Active Serial Header for JTAG or Active Serial interface. JTAG Interface Signals and Active Serial Signals from the SDM of Intel Agilex 7 SoC and FPGA is connected to the 10pin Header through a MUX switch. JTAG and Active Serial can be selected by toggling the POS 3 of the DIP Switch. The Intel Agilex 7 SoC and FPGA 's HPS and SDM share a common set of JTAG pins and each have their own TAP controller which are chained together inside the Intel Agilex 7 SoC and FPGA. These JTAG interface signals are at 1.8V Voltage level.

The JTAG/Active Serial Header is physically located on topside of the SOM as shown below. USB Blaster Programming Cable can be directly connected to this JTAG Header. JTAG interface signals are also connected to Board-to-Board Connector2 for access from Carrier board. The JTAG/AS Header (J4) is physically located on topside of the SOM as shown below.

Figure 4: JTAG/AS Header

Number of Pins - 10

Connector Part - GRPB052MWCN-RC from Sullins

Mating Connector - LPPB052NFSS-RC from Sullins

Table 7: JTAG/Active Serial Header Pinout- JTAG is selected.

| Pin No | Signal Name | Signal Type/<br>Termination | Description            |  |

|--------|-------------|-----------------------------|------------------------|--|

| 1      | JTAG_TCK    | I, 1.8V CMOS                | JTAG test Clock.       |  |

| 2      | GND         | Power                       | Ground.                |  |

| 3      | JTAG_TDO    | O, 1.8V CMOS                | JTAG test data output. |  |

| 4      | VCC(TRGT)   | Power                       | Target Power Supply    |  |

| Pin No | Signal Name | Signal Type/<br>Termination | Description                              |

|--------|-------------|-----------------------------|------------------------------------------|

| 5      | JTAG_TMS    | I, 1.8V CMOS/<br>10K PU     | JTAG test mode select.                   |

| 6      | JTAG_RESET  | I, 1.8V CMOS /10K<br>PU     | JTAG RESET. Not connected to SoC or FPGA |

| 7      | NC          | -                           | NC.                                      |

| 8      | NC          | -                           | NC.                                      |

| 9      | JTAG_TDI    | I, 1.8V CMOS/<br>10K PU     | JTAG test data input.                    |

| 10     | GND         | Power                       | Ground.                                  |

### Table 8: JTAG/Active Serial Header Pinout- Active Serial is selected.

| Pin No | Signal Name  | Signal Type/<br>Termination | Description                                        |

|--------|--------------|-----------------------------|----------------------------------------------------|

| 1      | AS_CLK       | I, 1.8V CMOS/10K PD         | Dedicated Serial clock to configure flash.         |

| 2      | GND          | Power                       | Ground.                                            |

| 3      | AS_CONF_DONE | IO, 1.8V OD                 | Configuration status IO to Intel Agilex 7 SoC and  |

|        |              |                             | FPGA.                                              |

| 4      | VCC(TRGT)    | Power                       | Target Power Supply                                |

| 5      | AS_nCONFIG   | I, 1.8V CMOS/10K PU         | Configuration input to Intel Agilex 7 SoC and FPGA |

| 6      | nCE          | I, 1.8V CMOS/10K PU         | Chip Enable input to Intel Agilex 7 SoC and FPGA   |

| 7      | AS_DO        | I, 1.8V CMOS                | Serial Data input to Configuration flash           |

| 8      | AS_CS0       | I, 1.8V CMOS/10K PU         | Chip select input to configuration flash.          |

| 9      | AS_DI        | O, 1.8V CMOS                | Serial Data output from configuration flash.       |

| 10     | GND          | Power                       | Ground.                                            |

### 2.5.2 Fan Header

The Intel Agilex 7 SoC and FPGA SOM supports a Fan Header (J3) to connect cooling Fan if required. The Fan Header (J3) is physically located on topside of the SOM as shown below.

Figure 5: Fan Header

Number of Pins - 2

Connector Part - 52125-02-0200-01 from CNC

Mating Connector - 52225-02 from CNC

**Table 9: Fan Header Pinout**

| Pin No | Signal Name | Signal Type/<br>Termination | Description     |

|--------|-------------|-----------------------------|-----------------|

| 1      | VCC_5V      | O, 5V Power                 | Supply Voltage. |

| 2      | GND         | Power                       | Ground.         |

The Intel Agilex 7 SoC and FPGA SOM supports three 240 pin high speed ruggedized terminal strip connectors for interfaces expansion. All the effort is made in Intel Agilex 7 SoC FPGA SOM design to provide the maximum interfaces of Intel Agilex 7 SoC and FPGA to the carrier board through these three Board to Board Connectors.

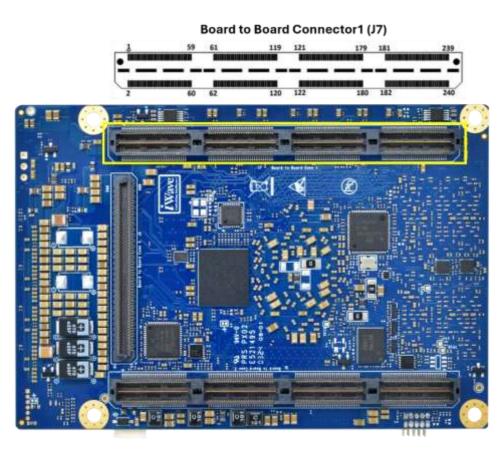

### 2.6 Board to Board Connector1

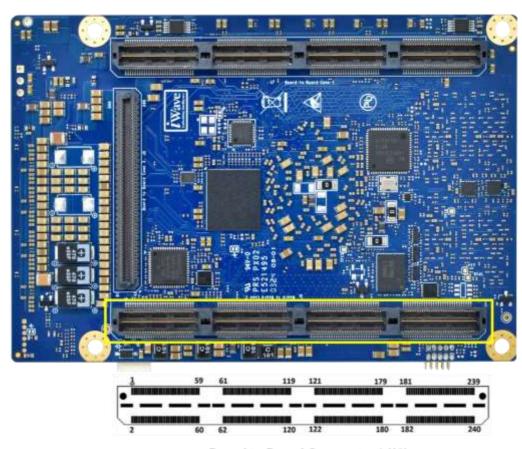

The Intel Agilex 7 SoC and FPGA SOM Board to Board Connector1 pinout is provided in the below table and the interfaces which are available at Board-to-Board Connector1 are explained in the following sections. The Board-to-Board Connector1 (J7) is physically located on bottom side of the SOM as shown below.

Figure 6: Board-to-Board Connector1

Number of Pins - 240

Connector Part Number - QTH-120-01-L-D-A from Samtech

Mating Connector - QSH-120-01-L-D-Afrom Samtech

Staking Height - 5mm

**Table 10: Board to Board Connector1 Pinout**

| Signal Name                | B2B-1 Pin | B2B-1 Pin | Signal Name                          |

|----------------------------|-----------|-----------|--------------------------------------|

| GND                        | 1         | 2         | GND                                  |

| FGTR13A_TX_Q0_CH0P         | 3         | 4         | REFCLK_FGTR13A_Q0_RX_CH0P            |

| FGTR13A_TX_Q0_CH0N         | 5         | 6         | REFCLK_FGTR13A_Q0_RX_CH0N            |

| GND                        | 7         | 8         | GND                                  |

| FGTR13A_TX_Q0_CH1P         | 9         | 10        | FPGA_B36_LVDS3A_12N_TX_IO49          |

| FGTR13A_TX_Q0_CH1N         | 11        | 12        | FPGA_E47_LVDS3A_3P_RX_IO86           |

| GND                        | 13        | 14        | FPGA_D48_LVDS3A_3N_RX_IO87           |

| FGTR13A_RX_Q0_CH1N         | 15        | 16        | FPGA_A47_LVDS3A_3P_TX_IO84           |

| FGTR13A_RX_Q0_CH1P         | 17        | 18        | FPGA_B48_LVDS3A_3N_TX_IO85           |

| GND                        | 19        | 20        | GND                                  |

| FGTR13A_RX_Q0_CH0N         | 21        | 22        | FPGA_F46_LVDS3A_5N_TX_IO77/CLKOUT_1N |

| FGTR13A_RX_Q0_CH0P         | 23        | 24        | FPGA_G45_LVDS3A_5P_TX_IO76/CLKOUT_1P |

| GND                        | 25        | 26        | GND                                  |

| FPGA_E53_LVDS3A_1P_RX_IO94 | 27        | 28        | FPGA_F50_LVDS3A_4N_RX_IO83           |

| FPGA_D54_LVDS3A_1N_RX_IO95 | 29        | 30        | FPGA_G49_LVDS3A_4P_RX_IO82           |

| FPGA_E51_LVDS3A_1P_TX_IO92 | 31        | 32        | FPGA_G47_LVDS3A_4P_TX_IO80           |

| FPGA_D52_LVDS3A_1N_TX_IO93 | 33        | 34        | FPGA_F48_LVDS3A_4N_TX_IO81           |

| GND                        | 35        | 36        | GND                                  |

| FGTR13A_TX_Q0_CH2P         | 37        | 38        | FPGA_J45_LVDS3A_5P_RX_IO78           |

| FGTR13A_TX_Q0_CH2N         | 39        | 40        | FPGA_K46_LVDS3A_5N_RX_IO79           |

| GND                        | 41        | 42        | FPGA_K44_LVDS3A_6N_RX_IO75           |

| FGTR13A_TX_Q0_CH3P         | 43        | 44        | FPGA_J43_LVDS3A_6P_RX_IO74           |

| FGTR13A_TX_Q0_CH3N         | 45        | 46        | FPGA_A45_LVDS3A_7P_TX_IO68           |

| GND                        | 47        | 48        | FPGA_B46_LVDS3A_7N_TX_IO69           |

| FGTR13A_RX_Q0_CH3N         | 49        | 50        | FPGA_A43_LVDS3A_8P_TX_IO64           |

| FGTR13A_RX_Q0_CH3P         | 51        | 52        | FPGA_B44_LVDS3A_8N_TX_IO65           |

| GND                        | 53        | 54        | GND                                  |

| FGTR13A_RX_Q0_CH2N         | 55        | 56        | FPGA_D46_LVDS3A_7N_RX_IO71/CLKIN_0N  |

| FGTR13A_RX_Q0_CH2P         | 57        | 58        | FPGA_E45_LVDS3A_7P_RX_IO70/CLKIN_0P  |

| GND                        | 59        | 60        | GND                                  |

| GND                        | 61        | 62        | GND                                  |

| NC                         | 63        | 64        | REFCLK_FGTR13A_Q0_RX_CH1P            |

| NC                         | 65        | 66        | REFCLK_FGTR13A_Q0_RX_CH1N            |

| GND                        | 67        | 68        | GND                                  |

| SDM_ADC_VSIGN_0            | 69        | 70        | FPGA_E41_LVDS3A_9P_RX_IO62           |

| SDM_ADC_VSIGP_0            | 71        | 72        | FPGA_D42_LVDS3A_9N_RX_IO63           |

| GND                        | 73        | 74        | FPGA_A41_LVDS3A_9P_TX_IO60           |

| NC                         | 75        | 76        | FPGA_B42_LVDS3A_9N_TX_IO61           |

| NC                         | 77        | 78        | NC                                   |

| GND                        | 79        | 80        | GND                                  |

| NC                         | 81        | 82        | FPGA_F44_LVDS3A_6N_TX_IO73/CLKIN_1N  |

| Signal Name                 | B2B-1 Pin | B2B-1 Pin | Signal Name                           |

|-----------------------------|-----------|-----------|---------------------------------------|

| NC                          | 83        | 84        | FPGA_G43_LVDS3A_6P_TX_IO72/CLKIN_1P   |

| GND                         | 85        | 86        | GND                                   |

| FPGA_E49_LVDS3A_2P_RX_IO90  | 87        | 88        | FPGA_D40_LVDS3A_10N_RX_IO59           |

| FPGA_D50_LVDS3A_2N_RX_IO91  | 89        | 90        | PCIE_PERST_N_13A_GXF                  |

| FPGA_A49_LVDS3A_2P_TX_IO88  | 91        | 92        | HPS_GPIO0_10_ETH_RST_N                |

| FPGA_B50_LVDS3A_2N_TX_IO89  | 93        | 94        | HPS_GPIO0_11_ETH_INT                  |

| GND                         | 95        | 96        | GND                                   |

| FGTR13A_TX_Q1_CH0P          | 97        | 98        | REFCLK_FGTR13A_Q1_RX_CH2P             |

| FGTR13A_TX_Q1_CH0N          | 99        | 100       | REFCLK_FGTR13A_Q1_RX_CH2N             |

| GND                         | 101       | 102       | GND                                   |

| FGTR13A_TX_Q1_CH1P          | 103       | 104       | NC                                    |

| FGTR13A_TX_Q1_CH1N          | 105       | 106       | NC                                    |

| GND                         | 107       | 108       | NC                                    |

| FGTR13A_RX_Q1_CH1N          | 109       | 110       | NC                                    |

| FGTR13A_RX_Q1_CH1P          | 111       | 112       | NC                                    |

| GND                         | 113       | 114       | GND                                   |

| FGTR13A_RX_Q1_CH0N          | 115       | 116       | FPGA_D44_LVDS3A_8N_RX_IO67/CLKOUT_0N  |

| FGTR13A_RX_Q1_CH0P          | 117       | 118       | FPGA_E43_LVDS3A_8P_RX_IO66/CLKOUT_0P  |

| GND                         | 119       | 120       | GND                                   |

| GND                         | 121       | 122       | GND                                   |

| FGTR13A_TX_Q1_CH2P          | 123       | 124       | HPS_MDIO1_MDC                         |

| FGTR13A_TX_Q1_CH2N          | 125       | 126       | HPS_MDIO1_MDIO                        |

| GND                         | 127       | 128       | NC                                    |

| FGTR13A_TX_Q1_CH3P          | 129       | 130       | FPGA_R41_LVDS3A_19P_RX_IO22/CLKIN_0P  |

| FGTR13A_TX_Q1_CH3N          | 131       | 132       | FPGA_P42_LVDS3A_19N_RX_IO23/CLKIN_0N  |

| GND                         | 133       | 134       | NC                                    |

| FGTR13A_RX_Q1_CH3N          | 135       | 136       | NC                                    |

| FGTR13A_RX_Q1_CH3P          | 137       | 138       | NC                                    |

| GND                         | 139       | 140       | GND                                   |

| FGTR13A_RX_Q1_CH2N          | 141       | 142       | FPGA_M46_LVDS3A_17N_TX_IO29/CLKOUT_1N |

| FGTR13A_RX_Q1_CH2P          | 143       | 144       | FPGA_L45_LVDS3A_17P_TX_IO28/CLKOUT_1P |

| GND                         | 145       | 146       | GND                                   |

| FPGA_W41_LVDS3A_13P_RX_IO46 | 147       | 148       | NC                                    |

| FPGA_Y42_LVDS3A_13N_RX_IO47 | 149       | 150       | NC                                    |

| FPGA_T42_LVDS3A_13N_TX_IO45 | 151       | 152       | NC                                    |

| FPGA_U41_LVDS3A_13P_TX_IO44 | 153       | 154       | NC                                    |

| GND                         | 155       | 156       | GND                                   |

| NC                          | 157       | 158       | REFCLK_FGTR13A_Q1_RX_CH3P             |

| NC                          | 159       | 160       | REFCLK_FGTR13A_Q1_RX_CH3N             |

| GND                         | 161       | 162       | GND                                   |

| SDM_ADC_VSIGN_1             | 163       | 164       | TEMPDIODE_12A_GXF_DP*                 |

| SDM_ADC_VSIGP_1             | 165       | 166       | TEMPDIODE_12A_GXF_DN*                 |

| Signal Name                 | B2B-1 Pin | B2B-1 Pin | Signal Name                 |

|-----------------------------|-----------|-----------|-----------------------------|

| GND                         | 167       | 168       | TEMPDIODE_13A_GXF_DN*       |

| Si_CLKGEN_REFIN_N*          | 169       | 170       | PCIE_PERST_N_12A_GXF        |

| Si_CLKGEN_REFIN_P*          | 171       | 172       | FPGA_L41_LVDS3A_19P_TX_IO20 |

| GND                         | 173       | 174       | GND                         |

| NC                          | 175       | 176       | FPGA_M40_LVDS3A_20N_TX_IO17 |

| NC                          | 177       | 178       | FPGA_L39_LVDS3A_20P_TX_IO16 |

| GND                         | 179       | 180       | GND                         |

| GND                         | 181       | 182       | GND                         |

| FGTR13A_TX_Q2_CH0P          | 183       | 184       | REFCLK_FGTR13A_Q2_RX_CH4P   |

| FGTR13A_TX_Q2_CH0N          | 185       | 186       | REFCLK_FGTR13A_Q2_RX_CH4N   |

| GND                         | 187       | 188       | GND                         |

| FGTR13A_TX_Q2_CH1P          | 189       | 190       | HPS_EMAC1_TX_CLK            |

| FGTR13A_TX_Q2_CH1N          | 191       | 192       | HPS_EMAC1_TXD0              |

| GND                         | 193       | 194       | HPS_EMAC1_TXD1              |

| FGTR13A_RX_Q2_CH1N          | 195       | 196       | HPS_EMAC1_TXD2              |

| FGTR13A_RX_Q2_CH1P          | 197       | 198       | HPS_EMAC1_TXD3              |

| GND                         | 199       | 200       | GND                         |

| FGTR13A_RX_Q2_CH0N          | 201       | 202       | NC                          |

| FGTR13A_RX_Q2_CH0P          | 203       | 204       | NC                          |

| GND                         | 205       | 206       | GND                         |

| FPGA_Y40_LVDS3A_14N_RX_IO43 | 207       | 208       | SOM_PWR_OK                  |

| FPGA_W39_LVDS3A_14P_RX_IO42 | 209       | 210       | HPS_EMAC1_TX_CTL            |

| FPGA_U39_LVDS3A_14P_TX_IO40 | 211       | 212       | HPS_EMAC1_RX_CLK            |

| FPGA_T40_LVDS3A_14N_TX_IO41 | 213       | 214       | HPS_EMAC1_RX_CTL            |

| GND                         | 215       | 216       | GND                         |

| FGTR13A_TX_Q2_CH2P          | 217       | 218       | REFCLK_FGTR13A_Q2_CH8P      |

| FGTR13A_TX_Q2_CH2N          | 219       | 220       | REFCLK_FGTR13A_Q2_CH8N      |

| GND                         | 221       | 222       | GND                         |

| FGTR13A_TX_Q2_CH3P          | 223       | 224       | HPS_EMAC1_RXD0              |

| FGTR13A_TX_Q2_CH3N          | 225       | 226       | HPS_EMAC1_RXD1              |

| GND                         | 227       | 228       | HPS_EMAC1_RXD2              |

| FGTR13A_RX_Q2_CH3N          | 229       | 230       | HPS_EMAC1_RXD3              |

| FGTR13A_RX_Q2_CH3P          | 231       | 232       | SOMPWR_EN                   |

| GND                         | 233       | 234       | GND                         |

| FGTR13A_RX_Q2_CH2N          | 235       | 236       | NC                          |

| FGTR13A_RX_Q2_CH2P          | 237       | 238       | NC                          |

| GND                         | 239       | 240       | GND                         |

| *Ontional                   |           |           |                             |

<sup>\*</sup>Optional

### 2.6.1 FPGA Interfaces

The interfaces which are supported in Board-to-Board Connector1 from Intel Agilex 7 SoC and FPGA is explained in the following section.

### 2.6.2 FPGA High Speed Transceivers

The Intel Agilex 7 SoC and FPGA SOM supports 12 high speed transceiver channels (12 Channels from FGT 13A Bank Quad [2:0] and Each quad supports 4 Transceiver channels) on Board-to-Board connector1. In Intel Agilex 7 SoC and FPGA SOM, the Transceivers connected to Board-to-Board Connector1 is capable of running up to a maximum speed of 32Gbps in NRZ Format or 58Gbps in PAM4 Format. These transceivers can be used to interface to multiple high-speed interface protocols. Each 4 Channel Transceiver Bank supports two reference clock input pairs.

Note1: FGT Quad0 can only support 20-32 Gbps PAM4. FGT Quad1, Quad2, and Quad3 can support 20-58 Gbps PAM4

Note2: Based on Device bank names will change. In this datasheet AGF 014 Device considered.

For more details on FGTL 13A transceiver pinouts on Board-to-Board Connector1, refer the below table.

| B2B-1<br>Pin No | B2B Connector1 Pin Name | CPU Ball Name/<br>Pin Number | Signal Type/<br>Termination | Description                                                           |

|-----------------|-------------------------|------------------------------|-----------------------------|-----------------------------------------------------------------------|

|                 |                         | BANK-FGT_13A Quad0 C         | hannels                     |                                                                       |

| 3               | FGTR13A_TX_Q0_CH0P      | FGTR13A_TX_Q0_CH0P/<br>AK4   | O, DIFF                     | Bank FGT13A-Q0 channel0 High speed differential transmitter positive. |

| 5               | FGTR13A_TX_Q0_CH0N      | FGTR13A_TX_Q0_CH0N/<br>AL5   | O, DIFF                     | Bank FGT13A-Q0 channel0 High speed differential transmitter negative. |

| 9               | FGTR13A_TX_Q0_CH1P      | FGTR13A_TX_Q0_CH1P/<br>AN7   | O, DIFF                     | Bank FGT13A-Q0 channel1 High speed differential transmitter positive. |

| 11              | FGTR13A_TX_Q0_CH1N      | FGTR13A_TX_Q0_CH1N/<br>AM8   | O, DIFF                     | Bank FGT13A-Q0 channel1 High speed differential transmitter negative. |

| 37              | FGTR13A_TX_Q0_CH2P      | FGTR13A_TX_Q0_CH2P/<br>AP4   | O, DIFF                     | Bank FGT13A-Q0 channel2 High speed differential transmitter positive. |

| 39              | FGTR13A_TX_Q0_CH2N      | FGTR13A_TX_Q0_CH2N/<br>AR5   | O, DIFF                     | Bank FGT13A-Q0 channel2 High speed differential transmitter negative. |

| 43              | FGTR13A_TX_Q0_CH3P      | FGTR13A_TX_Q0_CH3P/<br>AU7   | O, DIFF                     | Bank FGT13A-Q0 channel3 High speed differential transmitter positive. |

| B2B-1  | B2B Connector1                | CPU Ball Name/                     | Signal Type/ |                                                                                                                                               |  |  |

|--------|-------------------------------|------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin No | Pin Name                      | Pin Number                         | Termination  | Description                                                                                                                                   |  |  |

| 45     | FGTR13A_TX_Q0_CH3N            | FGTR13A_TX_Q0_CH3N/<br>AT8         | O, DIFF      | Bank FGT13A-Q0 channel3 High speed differential transmitter negative.                                                                         |  |  |

| 21     | FGTR13A_RX_Q0_CH0N            | FGTR13A_RX_Q0_CH0N/<br>AG5         | I, DIFF      | Bank FGT12A-Q0 channel0 High speed differential receiver negative.                                                                            |  |  |

| 23     | FGTR13A_RX_Q0_CH0P            | FGTR13A_RX_Q0_CH0P/<br>AF4         | I, DIFF      | Bank FGT12A-Q0 channel0 High speed differential receiver positive.                                                                            |  |  |

| 15     | FGTR13A_RX_Q0_CH1N            | FGTR13A_RX_Q0_CH1N/<br>AH2         | I, DIFF      | Bank FGT13A-Q0 channel1 High speed receiver negative.                                                                                         |  |  |

| 17     | FGTR13A_RX_Q0_CH1P            | FGTR13A_RX_Q0_CH1P/<br>AJ1         | I, DIFF      | Bank FGT13A-Q0 channel1 High speed differential receiver positive.                                                                            |  |  |

| 55     | FGTR13A_RX_Q0_CH2N            | FGTR13A_RX_Q0_CH2N/<br>AM2         | I, DIFF      | Bank FGT13A-Q0 channel2 High speed differential receiver negative.                                                                            |  |  |

| 57     | FGTR13A_RX_Q0_CH2P            | FGTR13A_RX_Q0_CH2P/<br>AN1         | I, DIFF      | Bank FGT13A-Q0 channel2 High speed differential receiver positive.                                                                            |  |  |

| 49     | FGTR13A_RX_Q0_CH3N            | FGTR13A_RX_Q0_CH3N/<br>AT2         | I, DIFF      | Bank FGT13A-Q0 channel3 High speed differential receiver negative.                                                                            |  |  |

| 51     | FGTR13A_RX_Q0_CH3P            | FGTR13A_RX_Q0_CH3P/<br>AU1         | I, DIFF      | Bank FGT13A-Q0 channel3 High speed differential receiver positive.                                                                            |  |  |

| 4      | REFCLK_FGTR13A_Q0_<br>RX_CH0P | REFCLK_FGTR13A_Q0_R<br>X_CH0P/ BH8 | I, DIFF      | Bank FGT13A-Q0 High speed differential Clock0 positive. Regional reference clock, this clock can be used for 13A Bank Q0 and Q1 Transceivers. |  |  |

| 6      | REFCLK_FGTR13A_Q0_<br>RX_CH0N | REFCLK_FGTR13A_Q0_R<br>X_CH0N/ BJ7 | I, DIFF      | Bank FGT13A-Q0 High speed differential Clock0 negative. Regional reference clock, this clock can be used for 13A Bank Q0 and Q1 Transceivers. |  |  |