- Products

- Automotive

- Avionics

COTS Module

- Agilex 7 SmartNIC Card

- Zynq RFSoC ADC DAC PCIe Card

- ZU7/ZU5/ZU4 PCIe SmartNIC Card

- ZU19/17/11 PCIe SmartNIC Card

- PCIe Switch Module

- PCIe to SD 3.0 M.2 Module

- Kintex-7 PCIe Card

- Zynq ZU7/ZU5/ZU4 3U-VPX

- Virtex UltraScale+ 3U VPX

- Kintex UltraScale+ 3U VPX

- Zynq ZU19/17/11 3U VPX

- Kintex-7 3U VPX Card

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x16 FMC+ Module

- PCIe Gen3 x8 FMC Module

- Quad QSFP28 FMC+ Module

- FMC Add-On Cards

- IP Cores

- ODM Solutions

- Custom Design

- Company

Get a Quote

Please fill in the form and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Get in Touch

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Thank you for subscribing to our newsletter!

Documents

Documents

UDP/IP Core

UDP/IP Core

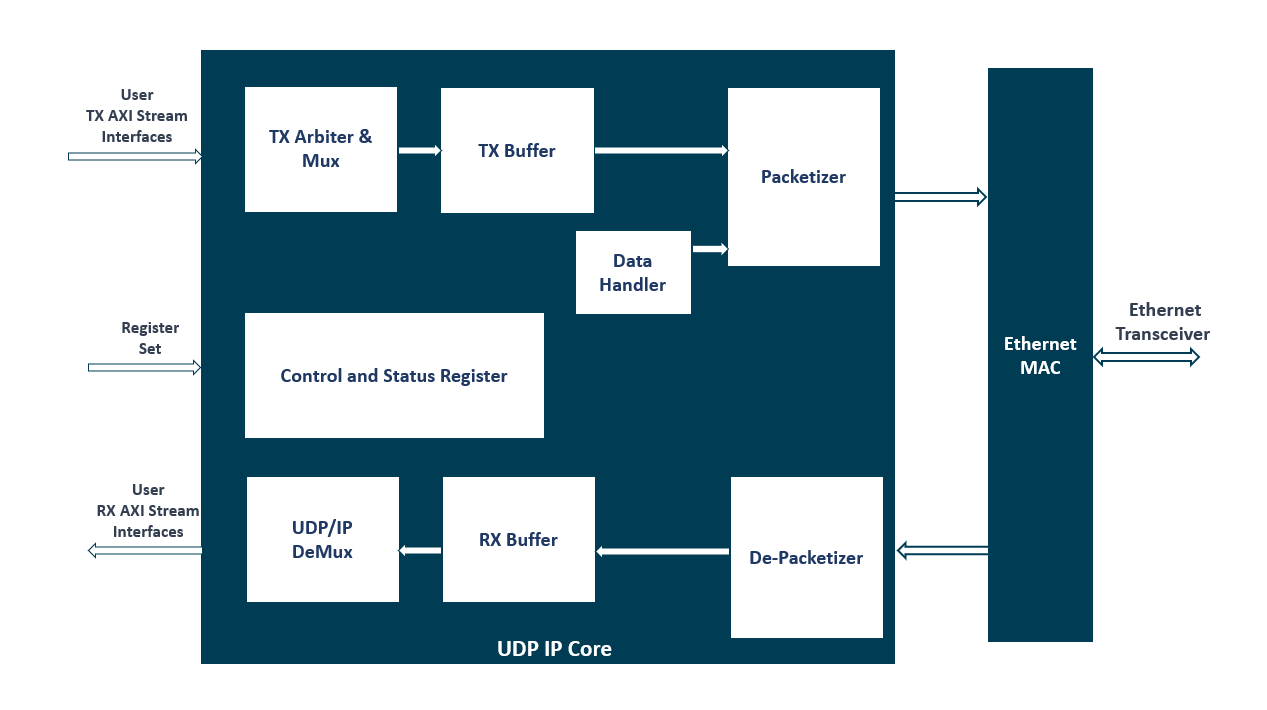

The UDP/IP Hardware protocol stack offloads UDP encapsulation task from the host processor enabling media streaming with speed up to 40G even in a processor less non-SoC designs, making it ideal for any standalone operation. This IP core provides an effective infrastructure to implement high-speed communication between the FPGA and other network devices. It supports easy to use AXI streams on the FPGA to connect to the network devices.

SPECIFICATION

- Easy integration with 1G, 10G, and 40G Ethernet MAC

- Configurable number of UDP Transmit & Receive channels from 1 to 32

- IPV4 support without packet fragmentation

- Supports GMII/RGMII/SGMII/XGMII/XLGRMII interfaces

- Echo-Request & Reply messages (“ping”) of the Internet Control Message Protocol (ICMP) used to test network connectivity

- Address Resolution Protocol (ARP) for proper functioning over the internet

- UDP & IP checksum generation and validation support

- 32bit, 64bit, and 128bit AXI stream interface for transmission & reception of user data and 32bit AXI4-Lite interface for handling control and status registers

- Configurable buffer sizes for easy SoC integration

- Supports optional Dynamic Host Configuration Protocol (DHCP) client

HIGHLIGHTS

- Bring full UDP/IP connectivity to FPGAs even if no CPU is available

- Offload UDP/IP processing into programmable logic

- Enable media streaming with speed up to 40G

- Offers a configurable number of UDP transmit and receive channels.

RELATED VIDEOS

Download

Please fill in the form below to download the document.

Thanks for filling in the download form.

Request Document

Please fill in the form below and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

iWave is an embedded systems engineering and solutions company, designing solutions for the Industrial, Medical, Automotive and Avionics vertical markets, and building on our core competency of embedded expertise since 1999. Read More…

Newsletter

Copyright © 2022 iWave Systems Technologies Pvt. Ltd.