- Products

- Automotive

- Avionics

COTS Module

- Agilex 7 SmartNIC Card

- Zynq RFSoC ADC DAC PCIe Card

- ZU7/ZU5/ZU4 PCIe SmartNIC Card

- ZU19/17/11 PCIe SmartNIC Card

- PCIe Switch Module

- PCIe to SD 3.0 M.2 Module

- Kintex-7 PCIe Card

- Zynq ZU7/ZU5/ZU4 3U-VPX

- Virtex UltraScale+ 3U VPX

- Kintex UltraScale+ 3U VPX

- Zynq ZU19/17/11 3U VPX

- Kintex-7 3U VPX Card

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x16 FMC+ Module

- PCIe Gen3 x8 FMC Module

- Quad QSFP28 FMC+ Module

- FMC Add-On Cards

- IP Cores

- ODM Solutions

- Custom Design

- Company

Get a Quote

Please fill in the form and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Get in Touch

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Thank you for subscribing to our newsletter!

Documents

Evaluation Platforms

Accessories

Additional Details

Documents

Evaluation Platforms

Accessories

Additional Details

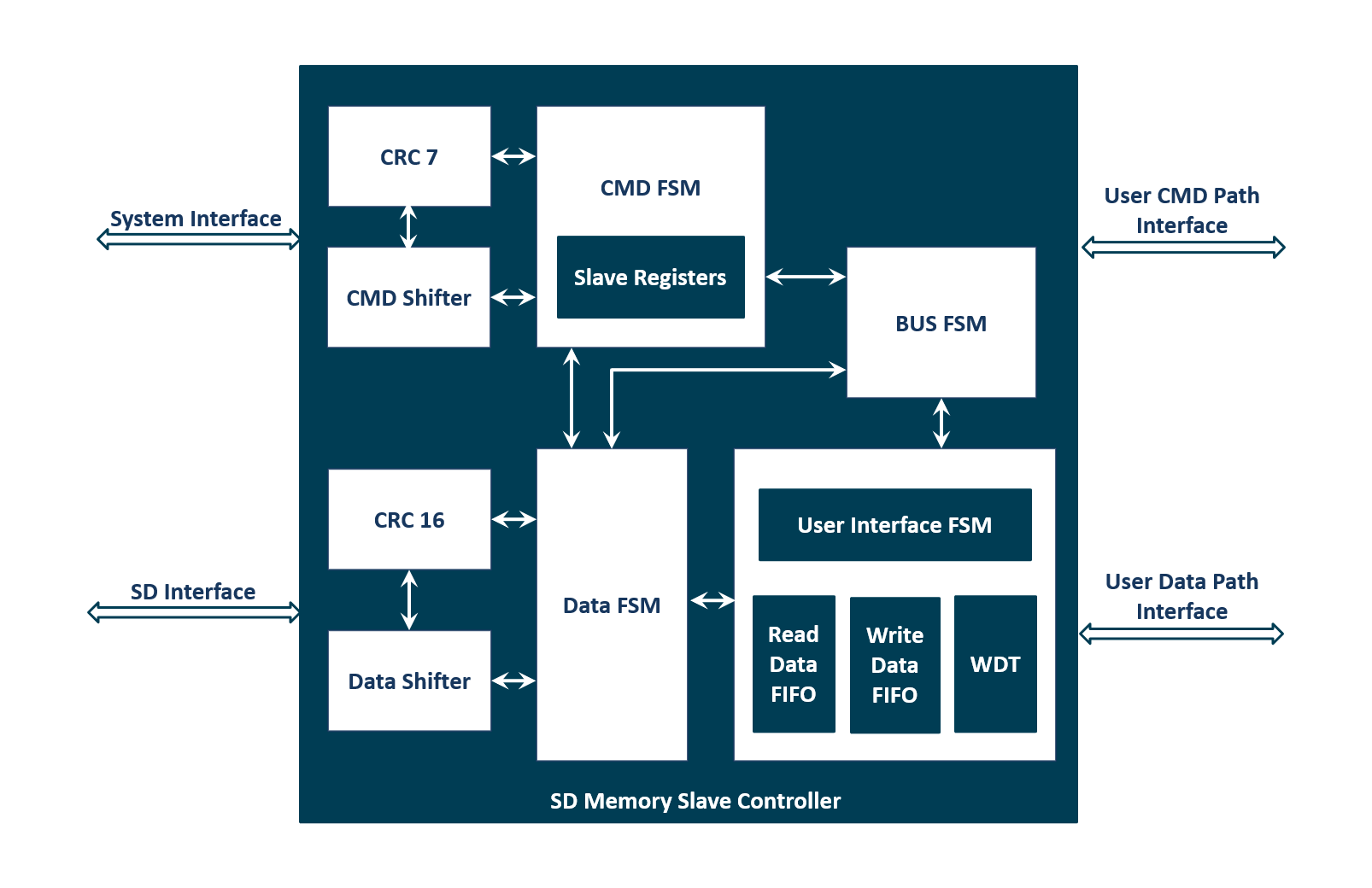

SD Memory Slave Controller

SD Memory Slave Controller

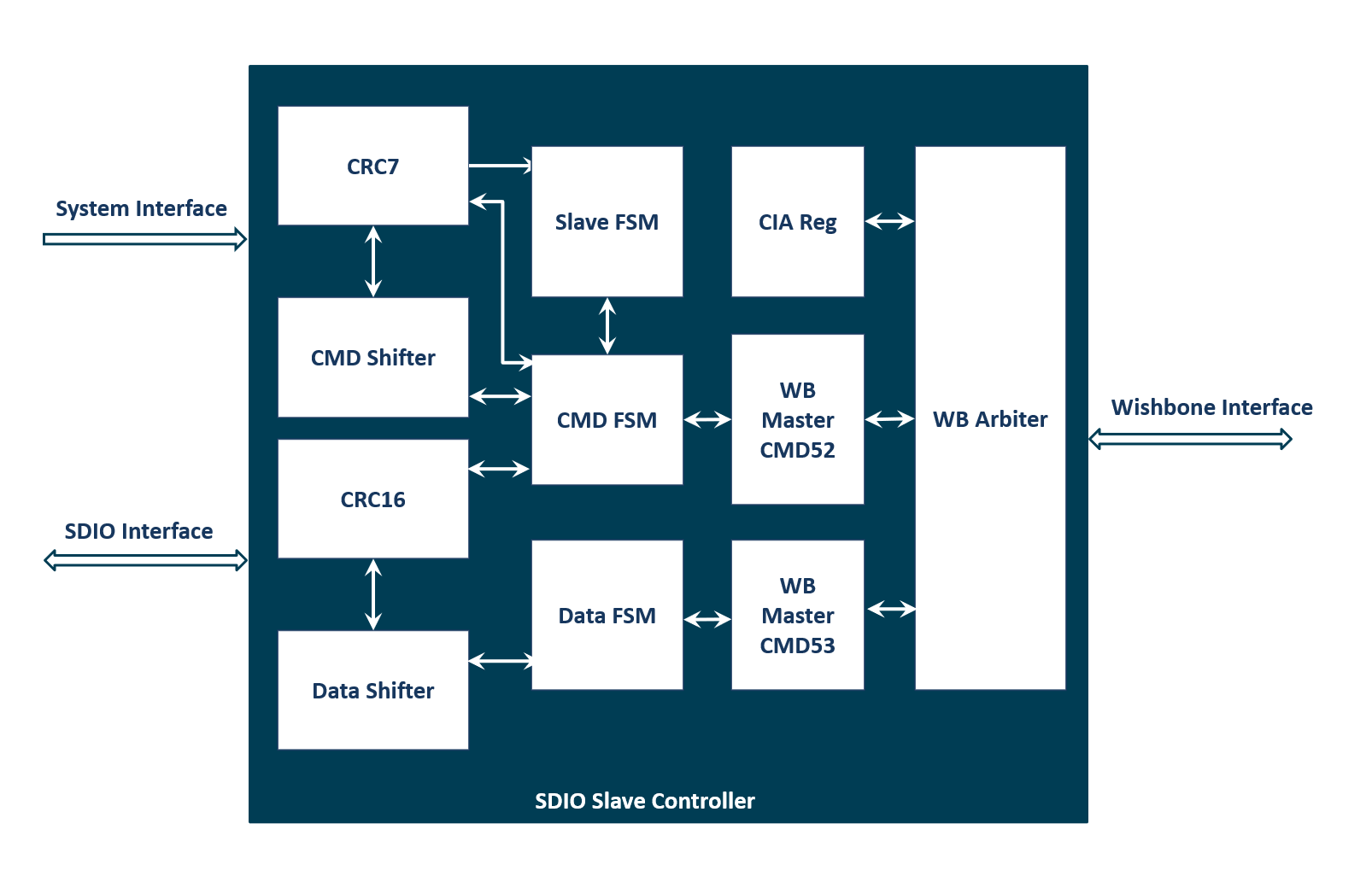

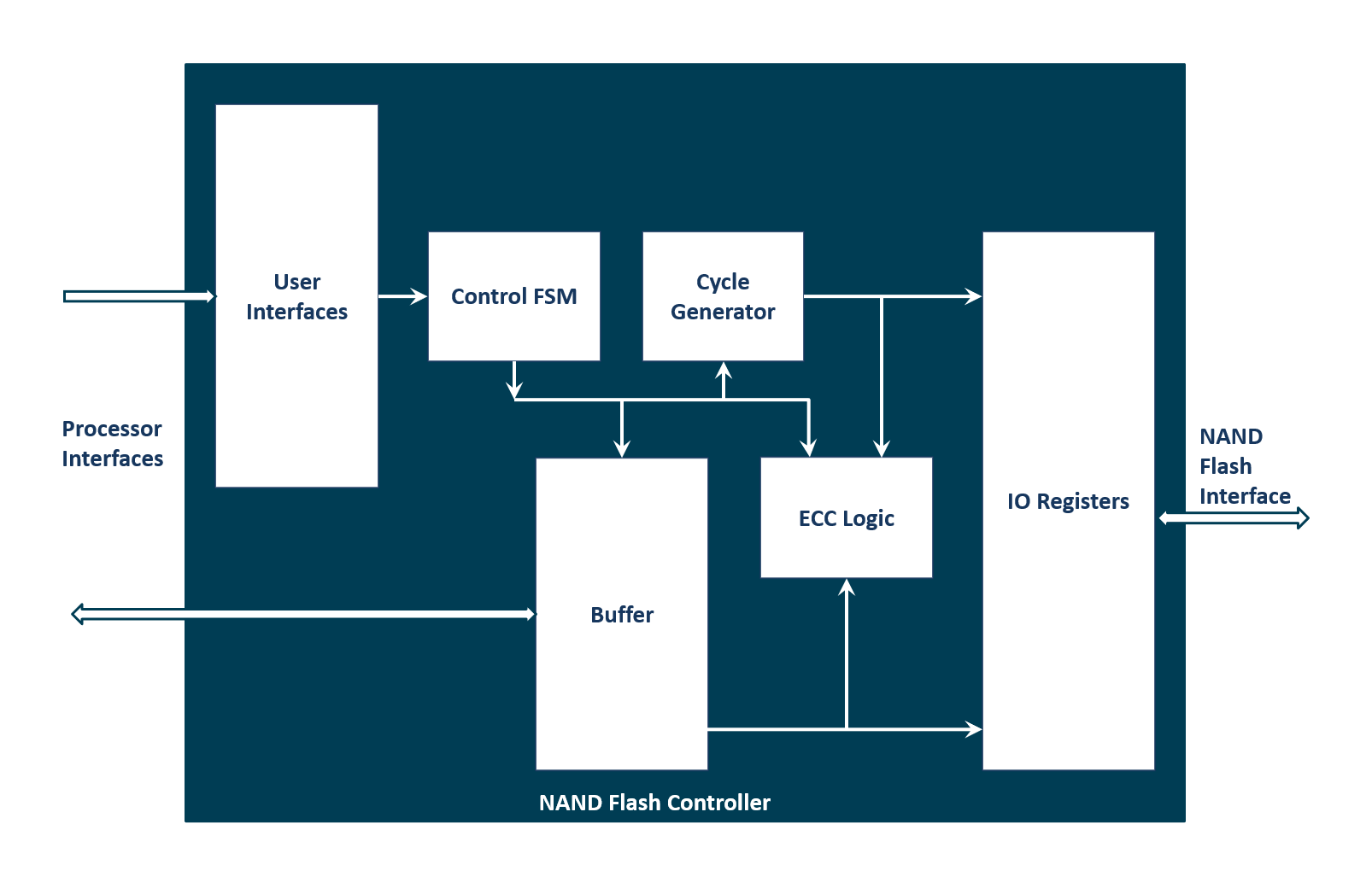

Memory Slave Controller IP forms a bridge between the SD host and user interface, enabling the data transfer between each other. This IP will send the response to the SD host depending on the command issued and also communicates with the user through a register interface for control and status. The Controller has two different variants depending on the availability of the processor towards user side. One being the AXI4 -lite or AHB complaint interface for accessing through processor and other is simple general-purpose interface which can be used without the processor.

SPECIFICATION

- Compliant with SD Physical Specification Version 3.00

- Supports 1-bit and 4-bit SD Mode

- Supports Standard and High Capacity operations

- Supports Default and High Speed Modes of operation

- Supports all mandatory slave registers set

- CID Register fields are configured

- Supports only Standard command set

- Supports all mandatory SD Command Classes

- CRC7 checking/generation for Command/Response

- CRC16 checking/generation for Data transfer

- Support Maximum block length of 512 bytes

- Supports Single and Multiple block read and write data transfer

- Supports Partial and Misalign Block length option

- SD Memory only implementation

- IP provides simple and general-purpose interface or AXI4-lite or AHB interface to user application

HIGHLIGHTS

- Core handles SD bus protocol on the card interface and provides simplified interface to user logic

- Core handle all the housekeeping tasks by itself without user logic intervention

- Supports both processor and non-processor environments with two different variants

- Supports both the standard and High capacity operation

EVALUATION PLATFORMS

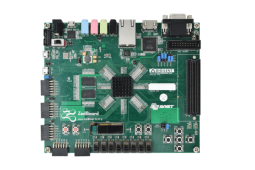

ZED Board

SD memory slave IP is tested in Zynq 7000 based devices from AMD/Xilinx using ZED Board and PMOD SD to interface with SD host using SD male to male custom cable. The baremetal version with DDR connected to FPGA targeted as memory variant of the IP is tested in this setup.

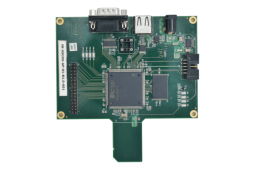

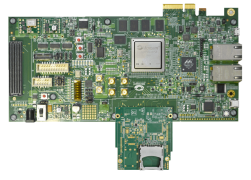

iWave ProASIC3 custom dev kit

SD memory slave IP is tested in ProASIC3 based devices from Microchip using iWave’s ProASIC3 custom dev kit which has the built in SD connector to interface with SD host. The simple user Interface with Block RAM of FPGA targeted as memory variant of the IP is tested in this setup.

SmartFusion2 Advanced Dev Kit

SD memory slave IP is tested in SmartFusion 2 based devices from Microchip using SmartFusion2 Advanced Development Kit (M2S150-ADV-DEV-KIT) and iWave FMC daughter card with SD to interface with SD host using SD male to male custom cable. The simple user Interface with Block RAM of FPGA targeted as memory variant of the IP is tested in this setup.

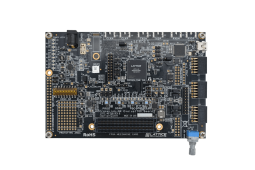

Lattice Crosslink NX dev kit

SD memory slave IP is tested in Crosslink NX based devices from Lattice using Crosslink NX dev kit and PMOD SD to interface with SD host using SD male to male custom cable. The simple user Interface with Block RAM of FPGA targeted as memory variant of the IP is tested in this setup.

RELATED VIDEOS

Related products

Download

Please fill in the form below to download the document.

Thanks for filling in the download form.

Request Document

Please fill in the form below and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

iWave is an embedded systems engineering and solutions company, designing solutions for the Industrial, Medical, Automotive and Avionics vertical markets, and building on our core competency of embedded expertise since 1999. Read More…

Newsletter

Copyright © 2022 iWave Systems Technologies Pvt. Ltd.