- Products

- Automotive

- Avionics

COTS Module

- Agilex 7 SmartNIC Card

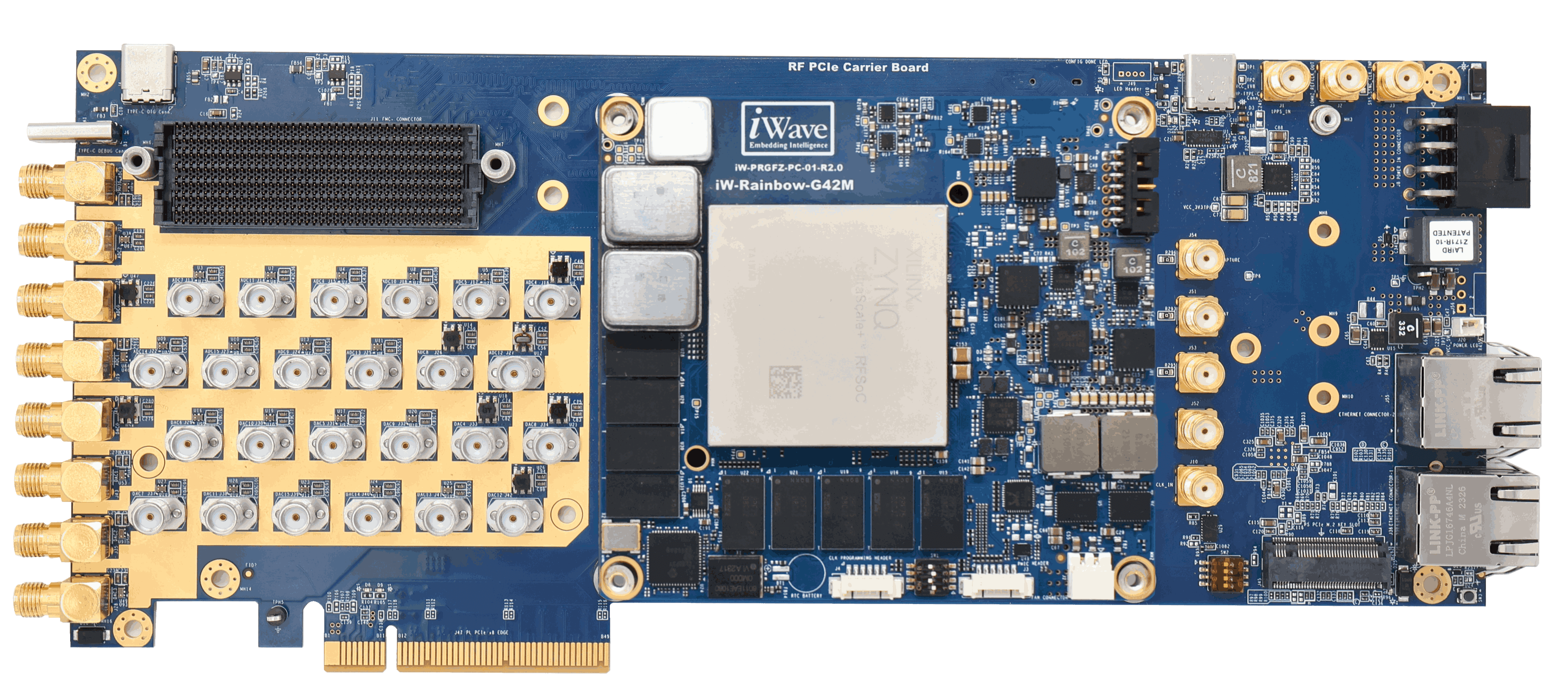

- Zynq RFSoC ADC DAC PCIe Card

- ZU7/ZU5/ZU4 PCIe SmartNIC Card

- ZU19/17/11 PCIe SmartNIC Card

- PCIe Switch Module

- PCIe to SD 3.0 M.2 Module

- Kintex-7 PCIe Card

- Zynq ZU7/ZU5/ZU4 3U-VPX

- Virtex UltraScale+ 3U VPX

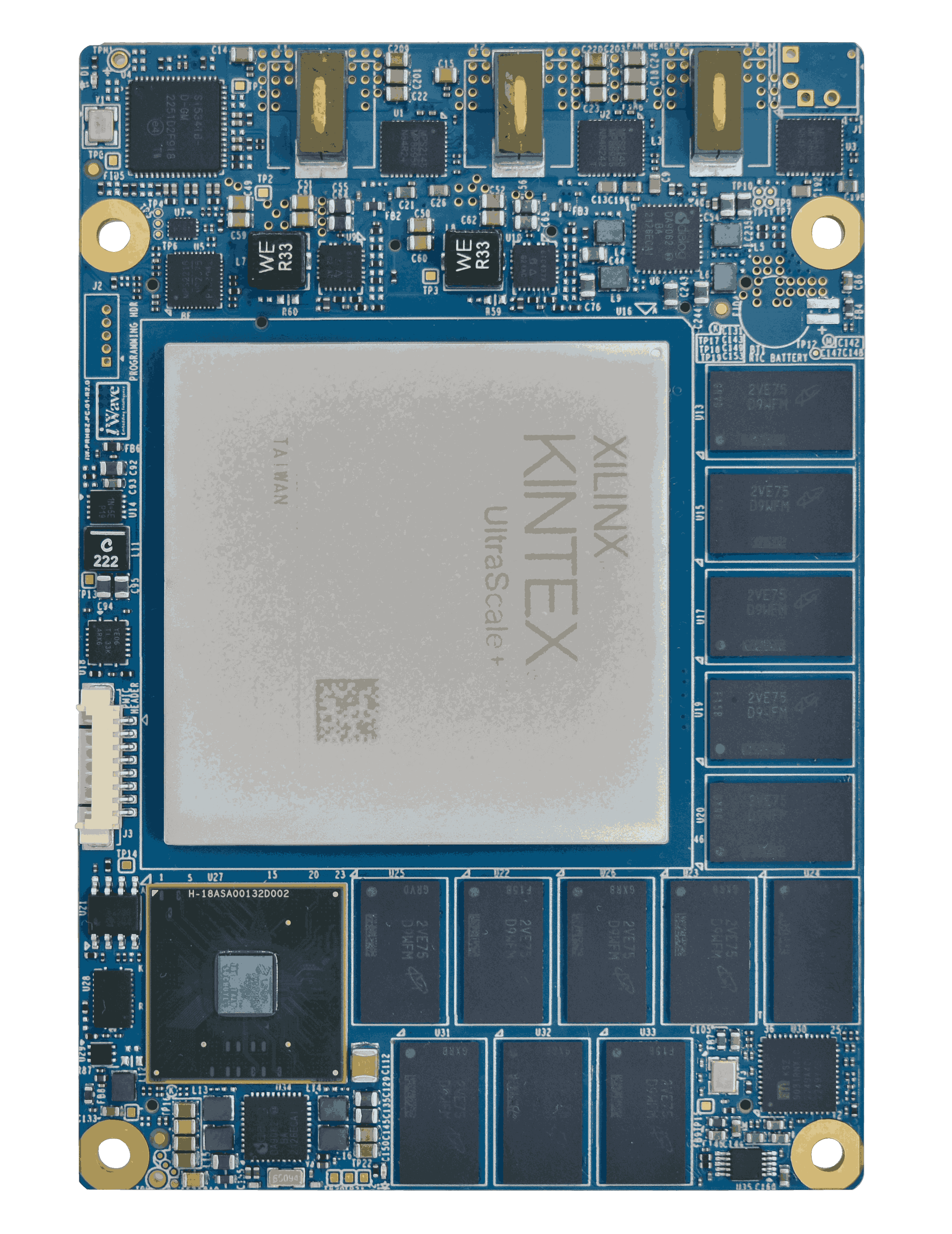

- Kintex UltraScale+ 3U VPX

- Zynq ZU19/17/11 3U VPX

- Kintex-7 3U VPX Card

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x16 FMC+ Module

- PCIe Gen3 x8 FMC Module

- Quad QSFP28 FMC+ Module

- FMC Add-On Cards

- IP Cores

- ODM Solutions

- Custom Design

- Company

Get a Quote

Please fill in the form and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Get in Touch

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Thank you for subscribing to our newsletter!

Design Support

Software

Design Support

Software

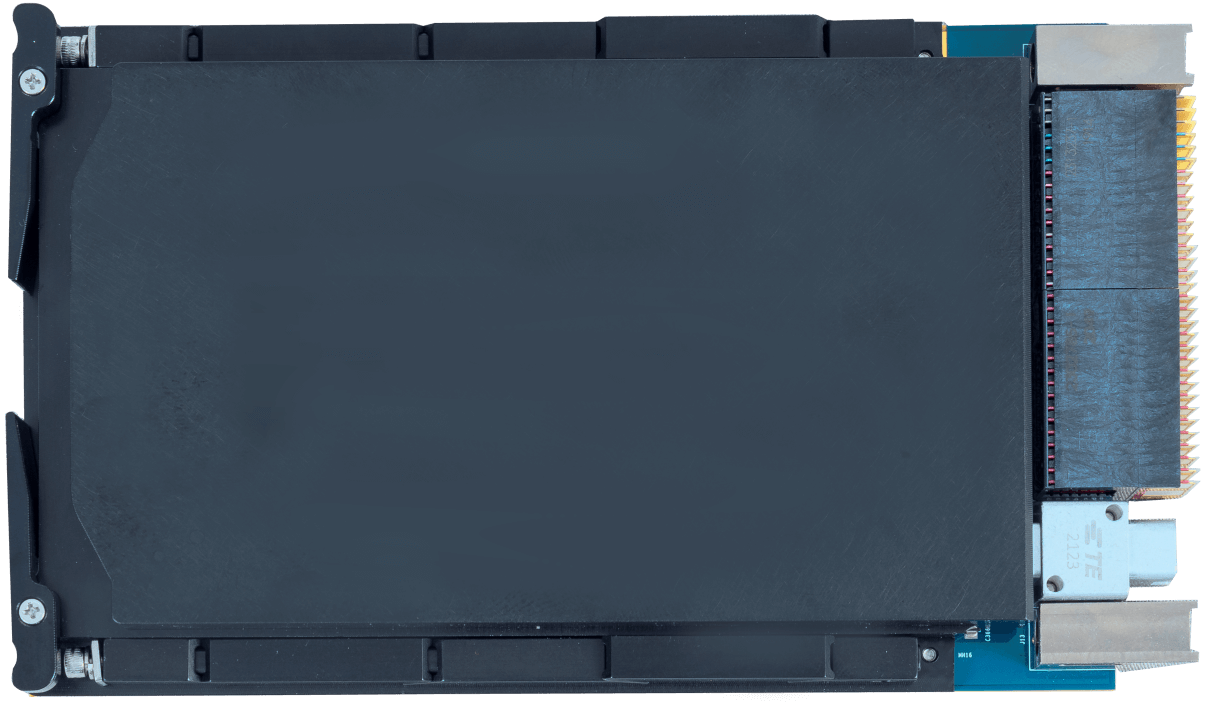

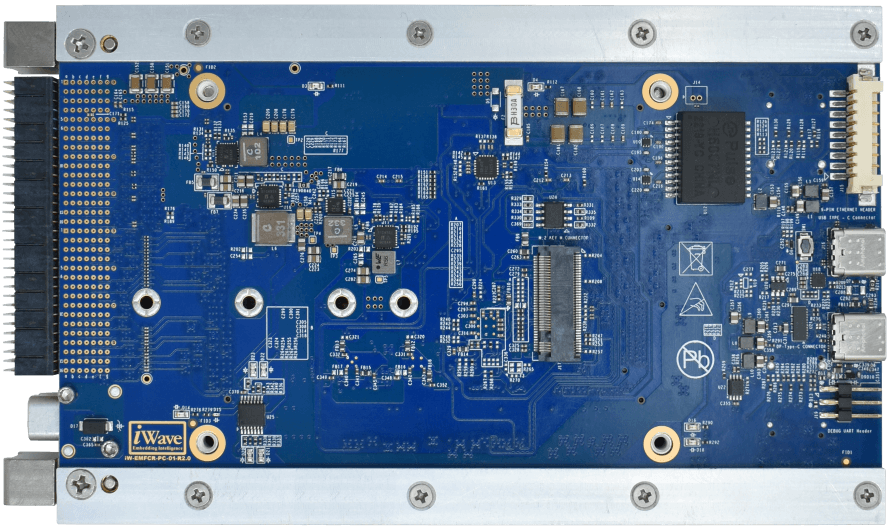

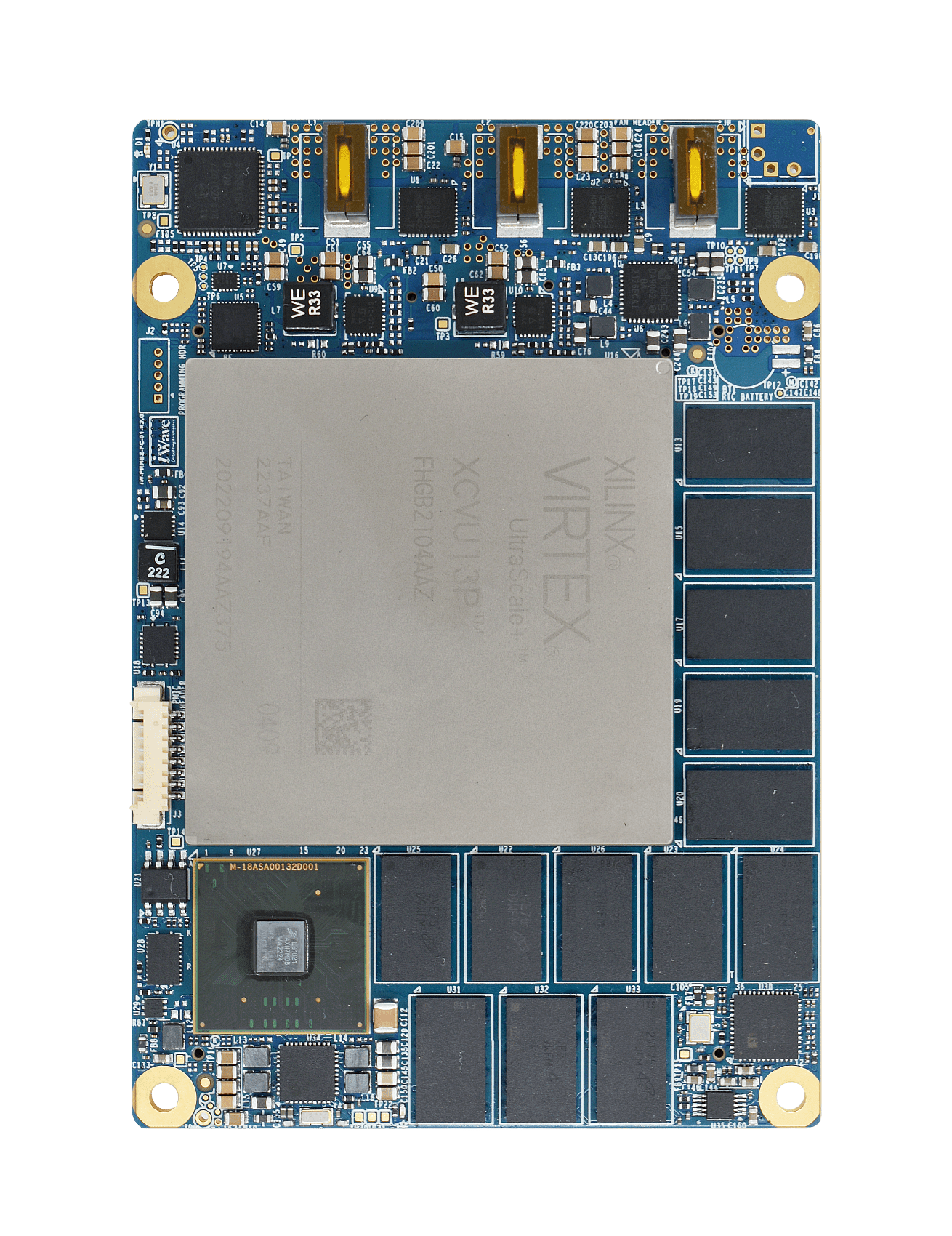

KU19P Kintex UltraScale+ 3U VPX Plug-in Module

KU19P Kintex UltraScale+ 3U VPX Plug-in Module

- AMD Xilinx’s KU19P, KU095, KU115 Kintex UltraScale+ FPGA

- Dual 64 bit, 4GB FPGA-DDR4 with ECC (Upgradable)

- 31 channels of FPGA GTY transceivers up to 32.75Gbps1

- Dual ARM Cortex-A7 core processor of 1.2GHz speed

- 32bit 2GB DDR4 for CPU with ECC

- 128MB QSPI Flash & 256MB NOR Flash

- 3U VPX Connectors based on ANSI/VITA 46.30 (P0+P1A & P1B+P2A)

- 8 Optical transceivers through MT Ferrule Connector (P2B) based on VITA66.4

On-Board Features

| KU19P/KU095/KU115 - Kintex UltraScale+ | Programming Logic (FPGA)

|

|---|---|

| LS1021A - Arm CPU | Arm® Cortex®-A7 MPCore compliant with Armv7-A™ architecture |

| RAM Memory | PL/FPGA: Dual 64bit, 4GB DDR4 RAM (expandable up to 16GB) |

| On Board Flash/Storage | 16bit, 256MB NOR Flash |

| FPGA to CPU Interface | RGMII |

3U VPX Backplane Features

| 3U VPX Connector (P0+P1A) |

|

|---|---|

| 3U VPX Connector (P1B+P2A) |

|

| MT Ferrule Optical Connector - P2B |

|

3U VPX Front Panel Features

|

Other On-Board Features

|

General Specification

| Slot Pitch | 1 Inch Conduction Cooled |

|---|---|

| Power Supply | +12VDC +/- 5% input from VPX Connector |

| Form Factor | 3U VPX (160mm X 100mm) |

1 By default one GTY transceiver channel is connected with on-SOM PCIe transceiver.

Custom Design Sevices

iWave provides end-to-end ODM services, from concept to production, leveraging our in-house expertise in hardware design, software development, FPGA design, and mechanical enclosure design. The FPGA expertise at iWave includes RTL, high speed bus interface and transceivers, storage, video, networking, and high-speed ADC/DAC with the entire product lifecycle, from initial concept to mass production and ongoing support.

THERMAL SOLUTIONS

For any highly integrated FPGA VPX Plug-in Module, thermal design is a very important factor. iWave supports a VITA 65.0 compliant 3U Conduction Cooled Heat Spreader.

Related products

RELATED VIDEOS

Related products

Related News

Download

Please fill in the form below to download the document.

Thanks for filling in the download form.

Request Document

Please fill in the form below and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

KU19P Kintex UltraScale+ 3U VPX Plug-in Module

3U VPX Card

iWave is an embedded systems engineering and solutions company, designing solutions for the Industrial, Medical, Automotive and Avionics vertical markets, and building on our core competency of embedded expertise since 1999. Read More…

Newsletter

Copyright © 2022 iWave Systems Technologies Pvt. Ltd.