- Products

- Automotive

- Avionics

COTS Module

- Zynq RFSoC ADC DAC PCIe Card

- Agilex 7 SmartNIC Card

- ZU7/ZU5/ZU4 PCIe SmartNIC Card

- ZU19/17/11 PCIe SmartNIC Card

- Kintex-7 PCIe Card

- PCIe Switch Module

- PCIe to SD 3.0 M.2 Module

- Zynq ZU7/ZU5/ZU4 3U-VPX

- Virtex UltraScale+ 3U VPX

- Kintex UltraScale+ 3U VPX

- Zynq ZU19/17/11 3U VPX

- Kintex-7 3U VPX Card

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- PCIe Gen3 x8 FMC Module

- Quad QSFP28 FMC+ Module

- PCIe Gen4 x16 FMC+ Module

- FMC Add-On Cards

- IP Cores

- ODM Solutions

- Custom Design

- Company

Get a Quote

Please fill in the form and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Get in Touch

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Thank you for subscribing to our newsletter!

Documents

Xilinx Evaluation Kit

Intel Evaluation Kit

Mircochip Evaluation Kit

Documents

Xilinx Evaluation Kit

Intel Evaluation Kit

Mircochip Evaluation Kit

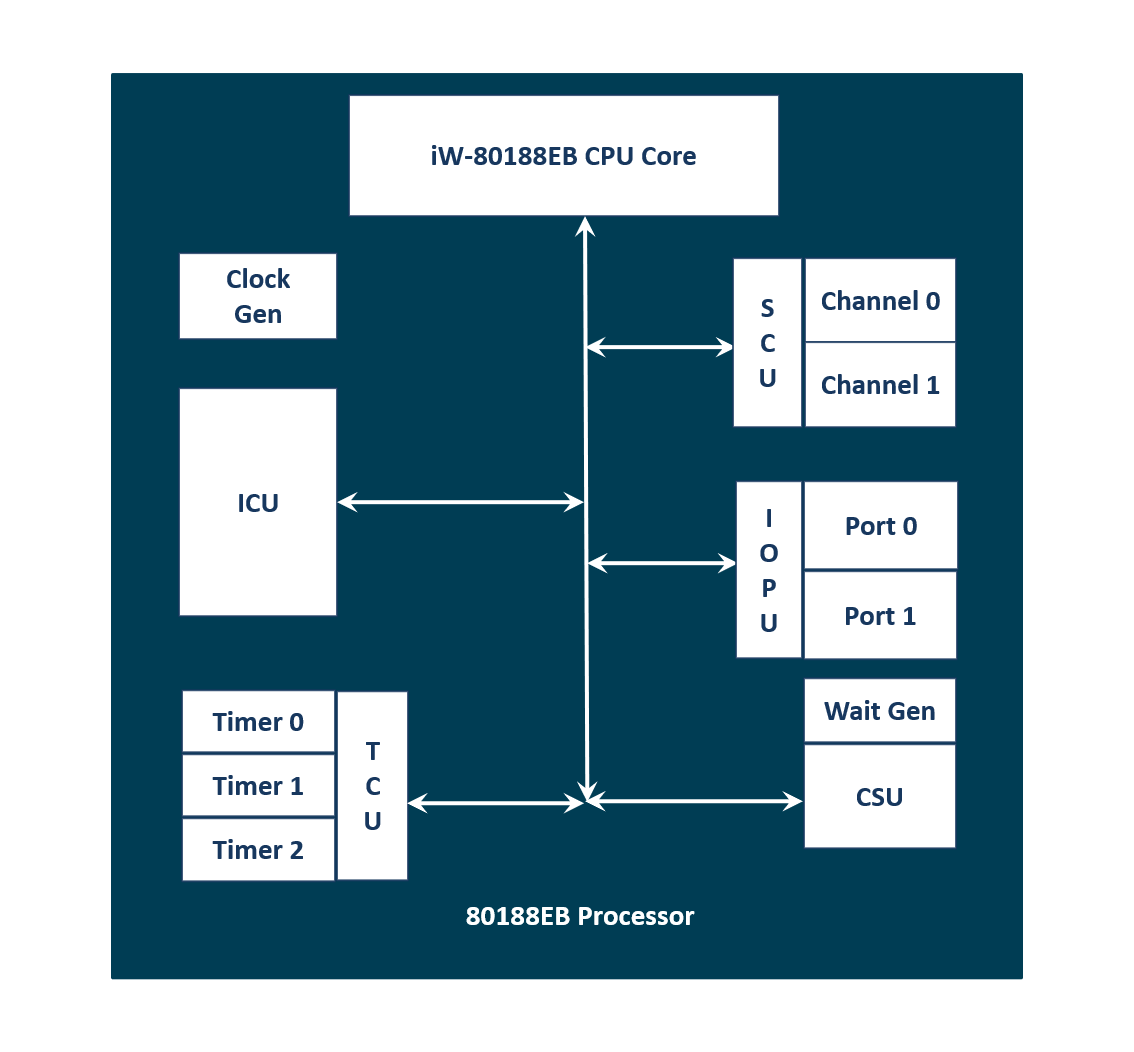

80188EB Processor

80188EB Processor

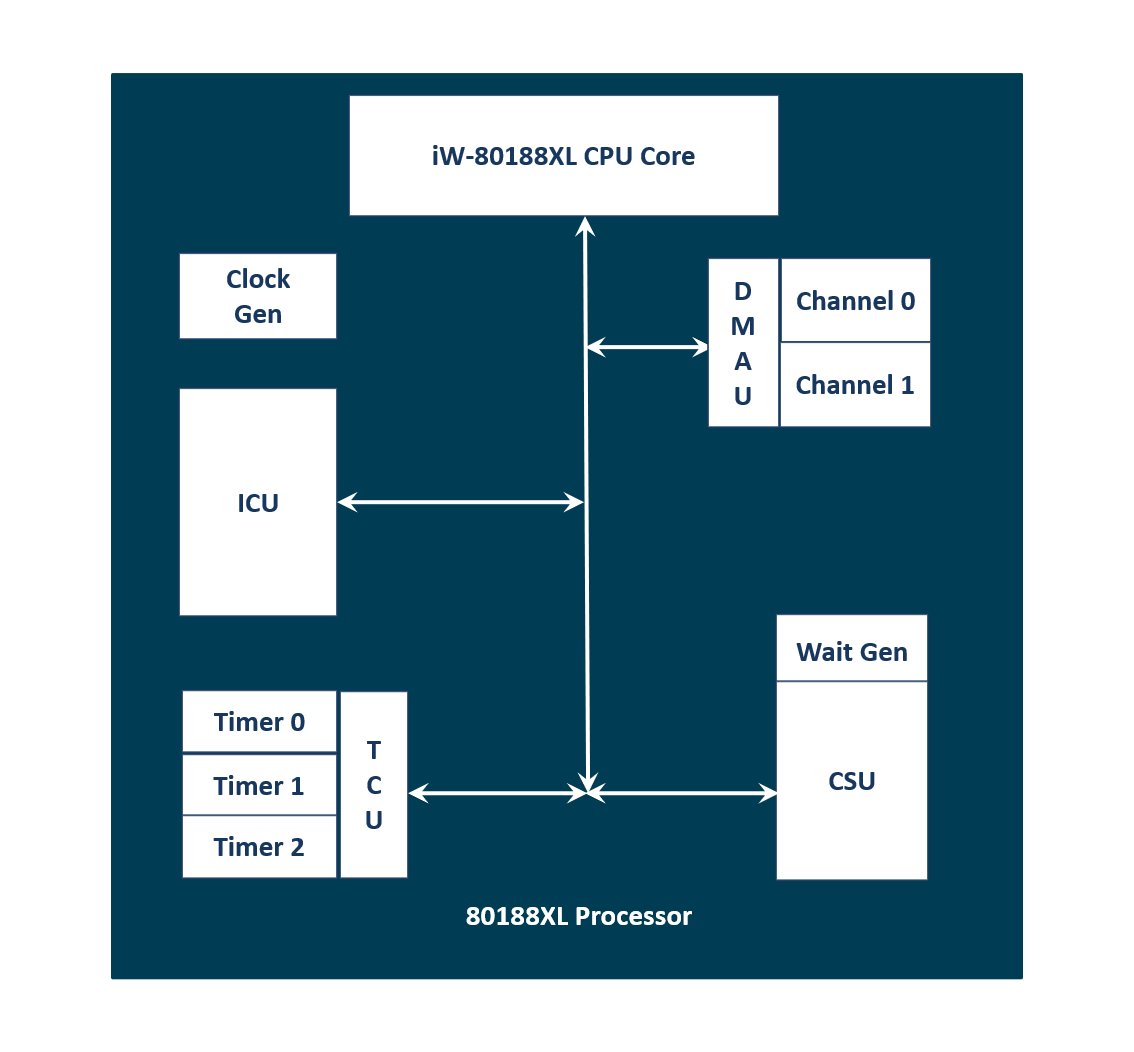

The 80188EB is a powerful 16-bit microprocessor core, executes instruction list compatible with 80188EB microprocessor. The 80188EB core has a broad set of integrated peripherals, which helps reduce system development time and cost and is compatible with wide range of compilers and debuggers. The design along with multiple peripherals can be fit into single FPGA.

Specification

- iW-80188EB CPU Core

- Multiplexed 20-bit address and 8-bit data bus

- 1M-byte memory space divided into 4 segments

- 64K-byte IO space

- Non Maskable Interrupt support

- Arithmetic-Logic Unit

- 8,16,32-bit arithmetic operations

- 8,16-bit logical operations

- Boolean manipulations

- 16 x 16 bit multiplication (signed or unsigned)

- 32/16-bit division (signed or unsigned)

- CPU On-Chip Peripherals

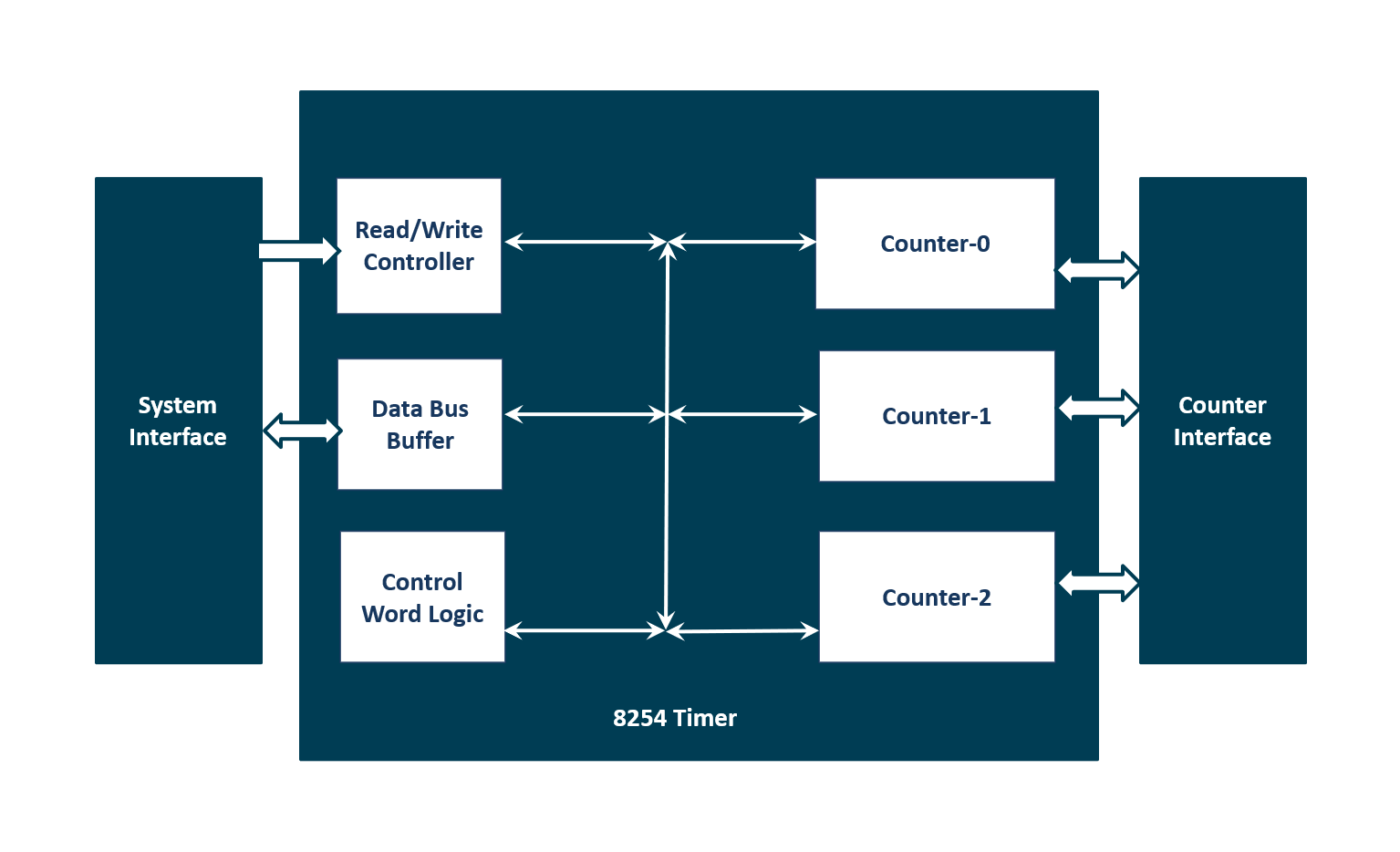

- Programmable Timer / Counter Unit

- Three programmable independent 16-bit timers

- TOUT0 to TOUT1 pin outputs

- TIN0 & TIN1 used either as clock or control signals

- Timer-2 can be used to clock other two timers

- Internal / external input clock selectable

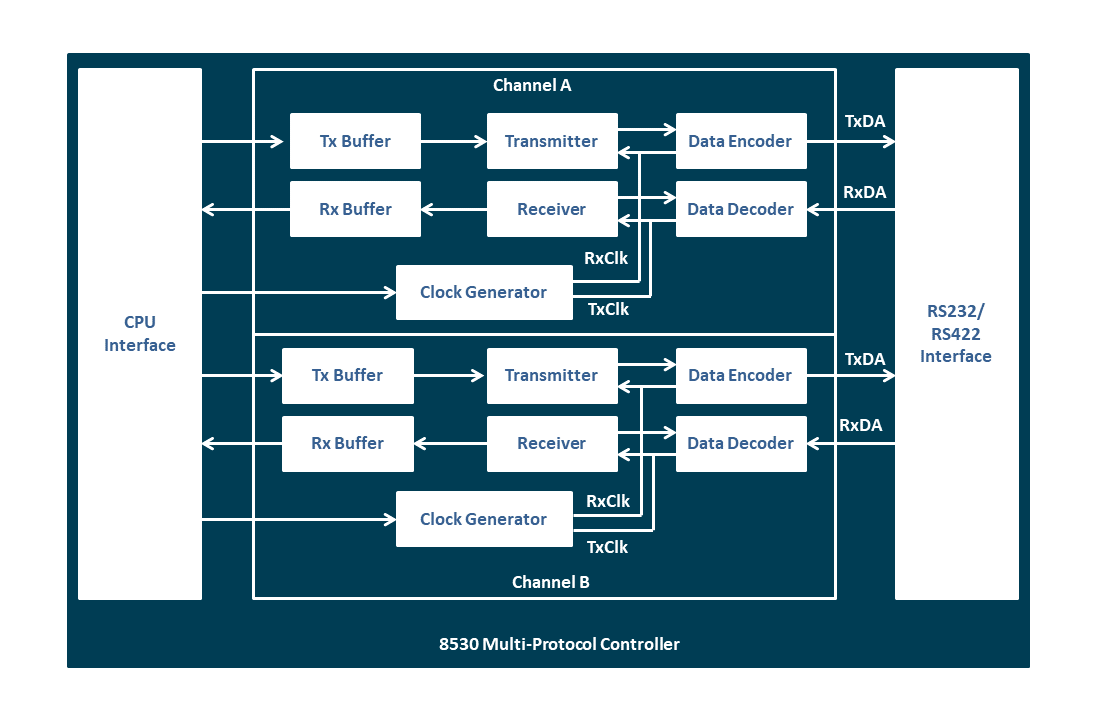

- Serial Communications Unit

- RS-232-C protocol support (on-chip CTS_N, SINT_N pins)

- Both synchronous and asynchronous modes are supported

- Two independent identical channels

- Full duplex operation in asynchronous mode

- Half-duplex operation in synchronous mode

- Programmable seven, eight or nine data bits in asynchronous mode

- Independent baud rate generator

- Double-buffered transmit and receive

- Clear-to-Send feature for transmission

- Break character transmission and detection

- Programmable even, odd or no parity

- Detects both framing and overrun errors

- Supports interrupt on transmit and receive

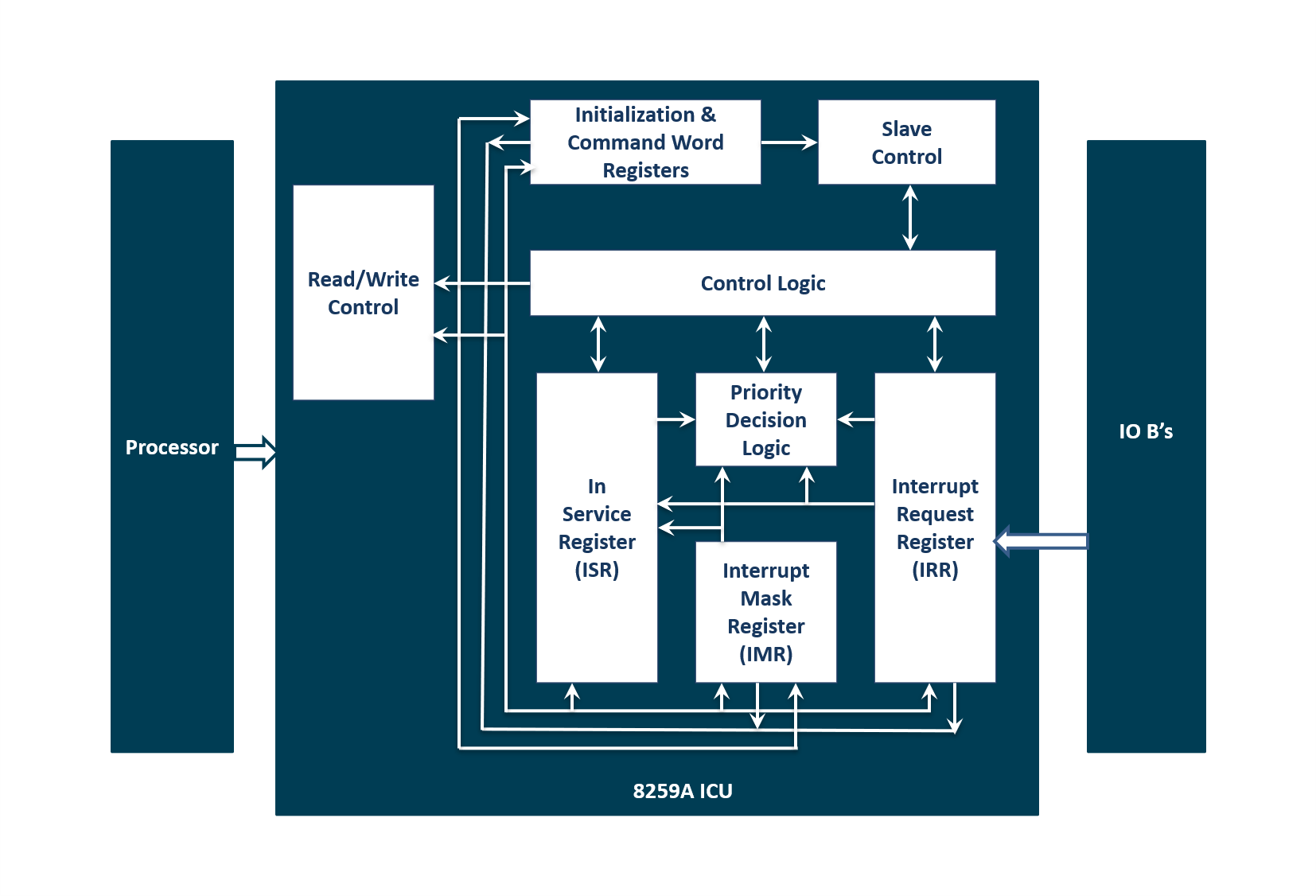

- Interrupt Controller Unit

- Edge trigger / level trigger selectable

- Individually maskable interrupt requests

- Programmable interrupt request priority orders

- Supports Cascading (Only INTP0 and INTP1) and polling mode

- 5 external interrupt request inputs (INTP0 to INTP4)

- 2 internal interrupt input pins (SCU and TCU)

- Chip Select Unit

- Ten programmable chip-select outputs

- Programmable start and stop addresses

- Memory or I/O bus cycle decoder

- Programmable wait-state generator

- Provision to disable a chip-select

- Provision to override bus ready

- Clock Generator

- Two 8-bit multiplexed Input/output Ports

- Programmable Timer / Counter Unit

- iW-80188EB CPU Core

HIGHLIGHTS

- Quick migration of 80188EB based designs to an FPGA platform

- Replacement for 80188EB processor and ASICs

RELATED VIDEOS

Related products

Download

Please fill in the form below to download the document.

Thanks for filling in the download form.

Request Document

Please fill in the form below and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

iWave is an embedded systems engineering and solutions company, designing solutions for the Industrial, Medical, Automotive and Avionics vertical markets, and building on our core competency of embedded expertise since 1999. Read More…

Newsletter

Copyright © 2022 iWave Systems Technologies Pvt. Ltd.