RISC-V: Open Standard Instruction Set Architecture on iWave's OSM

The two main CPU architectures commonly used in PCs, laptops, cellphones, and embedded devices around the world are x86 and ARM. These architectural designs demand licenses or royalties and are proprietary. They do not provide continual support, and they prevent businesses from creating their own ISAs (Instruction Set Architectures).

According to researchers, compilers in these architectures used only a subset of the instructions and included unnecessary decoding logic within the processors, resulting in high power consumption and area. The RISC-V processors overcame these constraints by condensing their instruction set and putting more resources into their registers.

Introduction to RISC-V Processor Architecture

RISC-V is an open standard instruction set architecture (ISA) established based on the RISC (Reduced Instruction Set Computing) design principles. It includes fewer sets of predefined instructions, which are easier to understand and code. As a result, RISC chips can perform millions of instructions per second (MIPS).

Unlike other ISA designs, RISC-V is available under an open-source license that delivers a new level of free, extensible software and hardware freedom on architecture. RISC-V is suitable for all computing systems, from a microcontroller to supercomputers, and there is no restriction on its implementation.

RISC-V provides a variety of advantages,

- Build new business models: Since RISC-V is a layered and extensible ISA, companies can build custom processors for advanced workloads by implementing minimal instruction sets, well-defined extensions, and custom extensions.

- Reduce risks and investments: Leverage shared tools and development resources from the development community to reduce risk and investment.

- Offers flexibility to customize processor: Since RISC-V architecture is implemented based on SoC composition and other design attributes, engineers can customize their chipsets to big, small, or powerful based on the device’s needs.

- Open source: RISC-V allows one to freely download design files from git repositories and use them to build hardware designs free of IP and licensing restrictions.

RISC architecture performs highly optimized operations at a fraction of the power compared to CISC. RISC processors execute simple instructions in a single clock cycle. On the contrary, CISC takes the opposite approach. As a result, RISC requires more clock cycles to perform the same instruction as in CISC but is more efficient and consumes less power. While CISC allows computers to execute more in a single instruction cycle, RISC allows simplified programming.

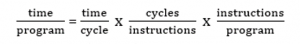

The equation below illustrates the link between computer performance (time required to run a program), cycles per instruction, and the total number of instructions in a program.

Computer performance comparison equation (Stanford University)

The equation states that program instructions are inversely proportional to device performance. To improve the performance of a device, one can minimize the number of clocks per instruction or reduce the number of instructions per program. In general, RISC architecture is more successful in reducing the overall power consumption and sometimes at the expense of low performance.

Within the RISC category, there are many different instructions set architectures, and ARM is one of the most popular ISAs among SoC suppliers. Since RISC-V is the newest member of the RISC family, the RISC-V instruction set architecture is gaining popularity and interest among the embedded sectors. Industry leaders are incorporating RISC ISA in their designs to meet multiple industries and applications, and Renesas is at the forefront of such initiatives. In March 2022, Renesas announced the RZ/FIVE general-purpose microprocessor units (MPUs) based on a 64-bit RISC-V CPU core.

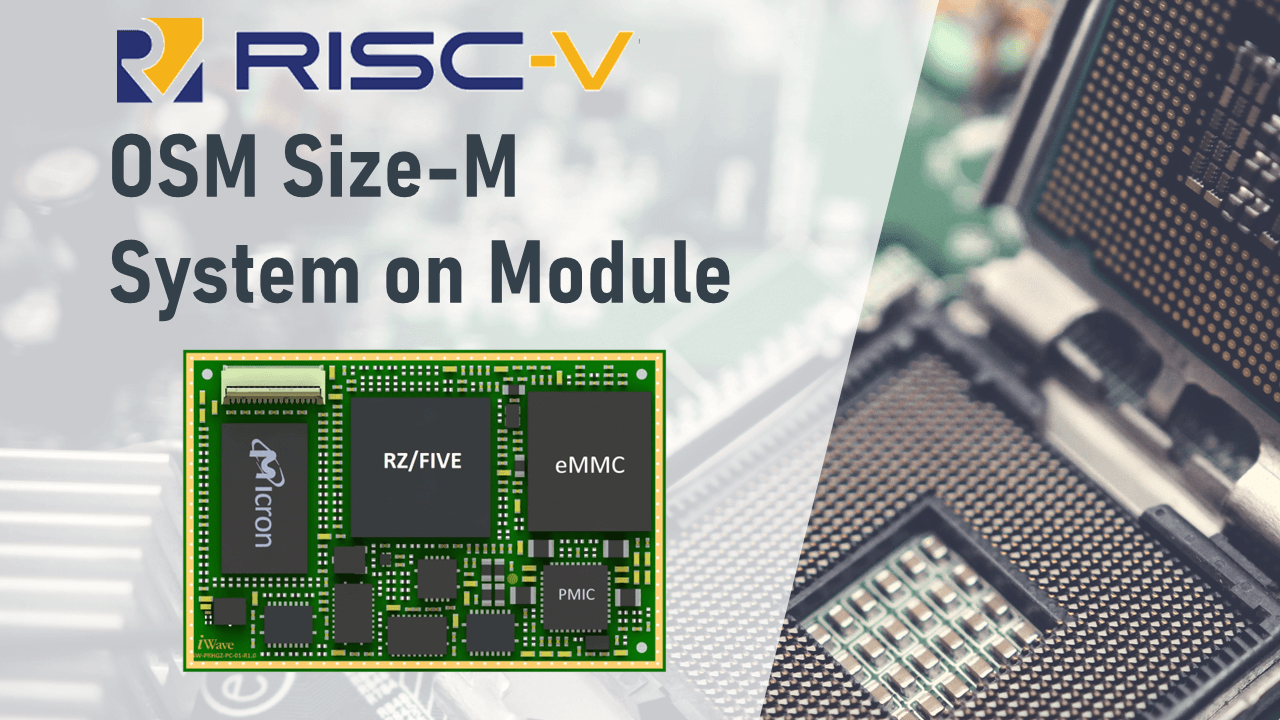

RISC-V based System on Modules

As a Renesas Synergy partner, iWave introduced yet another remarkable development on embedded platforms, realized by the powerful Renesas RZ/FIVE MPU-based System on Module targeting IoT endpoint devices such as gateways.

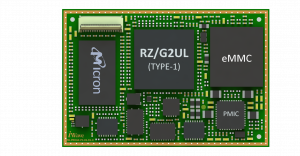

iW-RainboW-G53M System on Module is Renesas RZ/FIVE or RZ/G2UL or RZ/A3UL MPU-based LGA modules designed according to the Open Standard Module (OSM) Size-M Specification. The modules compatibility with the ARM Cortex-A55 and RISC-V architectures broadens customer choices and increases product development freedom.

Salient features of Renesas RZ/FIVE or RZ/G2UL or RZ/A3UL based System on Module are,

- Compatible with Renesas G2UL or A3UL or FIVE MPU

- Supports Cortex-A55 cores (G2UL & A3UL)

- Supports Cortex-M33 core for RTOS (G2UL)

- RISC-V Andes AX45MP @1.0GHz (FIVE)

- 2x RGMII, 2x USB 2.0, 1x MIPI CSI, 1x RGB

- 1GB DDR4 RAM

- OSM Size-SE LGA Module

Because the SoM is available in the OSM Size-M specification standard, it can be soldered directly onto the carrier board, adding an extra level of ruggedness to products prone to vibrations and requiring a compact form factor.

With its compact design and wide range of services, the RZ/Five SoM embeds low power consumption, thermal efficiency, and low cost into embedded systems.

For more information or inquiries, please contact mktg@iwavesystems.com.

Keep Reading

|  |  |

| Healthcare IoT using Renesas Synerghy | Strong security and end to end IoT gateways | Renesas RZ/G1H SoM with QNX 7.0 RTOS |