RPMsg Inter-Process Communication in iWave Portfolio of i.MX8 Solutions

RPMsg Inter Process Communication Enables Faster, Reliable and Secure Communications in iWave Portfolio of i.MX8 Solutions

With the growing trends in connected devices and the proliferation of IoT, there is an increasing requirement for multi-core processing systems that empower the acceleration of connected technologies. A leading example of a multicore system is the cutting edge i.MX8 series of processors by NXP that couples two high performance ARM cores- The Cortex-A and the Cortex M cores onto a single chip.NXP allows an advanced Remote Processor Messaging (RPMsg) mechanism for Inter Process Communication between the cores, which ensures faster throughput, reduced power, and enhanced system control in connected devices.

Inter Process Communication:

Inter Process Communication (IPC) is a mechanism that allows multiple cores of a heterogeneous processing system to communicate and share data with each other. IPC allows enhanced utilization of resources in a multi-processing environment such as the i.MX8 processor, which has the Cortex-A core designed to deliver complex processing and networking while the Cortex M cores accelerate real-time control.

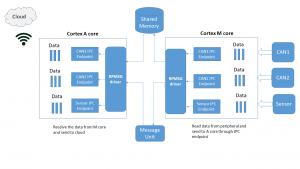

For instance, in an automotive use case, the Cortex-A can be used for performance-intensive operations such as running a powerful UI using non real-time OS such as Linux or Android whereas, the Cortex M core can handle real-time tasks such as data acquisition from sensors using RTOS like the FreeRTOS and RTA-OS. In such a case, both cores need to be synchronized and be able to communicate with each other efficiently. In i.MX8 this is achieved using the RPMsg messaging bus that allows the operational cores to exchange data via hardware message unit and shared memory unit.

Inter Process Communication (IPC) using RPMsg:

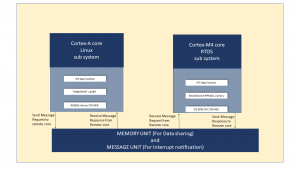

The Remote Processor Messaging mechanism uses a master-slave architecture where the A core acts as a master and M core as a slave. Notification of data to other core is enabled using the Message Unit interrupt notification while the shared Memory Unit is used to store and share data between the cores. In the RPMsg mechanism, any number of endpoints can be created, allowing parallel paths for sharing multiple data between the cores. The combined use of message unit and shared memory enables higher throughput and faster data transfer allowing rapid execution and control in multicore systems.

iWave has illustrated an advanced IPC usage through a bidirectional IPC demo featuring multiple endpoints communicating from M core to A core and vice versa. iWave has designed custom protocol and wrapper API to create each endpoint with a unique source and destination endpoint address. The source endpoint refers to A core endpoint for each peripheral, and destination endpoint refers to M core endpoint. To enable secure and reliable multi-endpoint transfer in i.MX8, we have utilized multiple threads to read/write data from the endpoints. iWave has built the expertise to configure additional message units that will accelerate the data exchange between the cores and ensure improved performance in i.MX8 platforms.

The above diagram illustrates iWave’s advanced IPC demo where the Cortex M core read CAN and sensor payload and sent it to the Cortex-A core using IPC endpoints.

iWave offers a wide range of embedded solutions based on the multi-core NXP i.MX 8 processors, including system on modules, SBCs, and end solutions. In addition to services on IPC implementations, iWave offers comprehensive hardware and software customization services for applications based on i.MX8 processors targeting Security, OTA, and telematics with a focus on helping customers accelerate their innovations by optimizing their design cycles and faster time to market.

Detailed information on iWave i.MX 8 module can be found here.

To get in touch with us for inquiries and further information, please write to mktg@iwavesystems.com or contact our Regional Partners