iWave announces the release of eMMC revision 5.1 achieving unrivalled speeds up to 3.2 Gb/s

The eMMC 5.1 specification defined by JEDEC enables the next level of high-speed data transfer and provides an easy migration & simplified system design for the next-gen products with its low pin count, high bandwidth, and multiple boot mechanism.

iWave’s eMMC 5.1 host controller IP is compliant with the latest eMMC specification. It includes all-new features including high-performance HS400 Enhanced strobe mode, HS400 mode, Command Queuing Engine (CQE), tuning of HS200 mode making data transfer highly efficient by offloading the software overhead into the controller, and others. Furthermore, it improves the system reliability of operation by utilizing the enhanced strobe at the PHY layer.

eMMC 5.1 host controller IP simplifies the system design by supporting power-on boot without the upper level of the software driver. The IP also provides an advanced high-performance AXI4 lite for register access and memory-mapped for DMA transfer to any System on Chip (SoC). eMMC 5.1 is backward compatible with previous versions of eMMC such as default speed (@26Mhz), high speed (@52 Mhz), and DDR52, 1-bit, 4-bit, and 8-bit eMMC modes and supports block lengths of up to 4096 bytes.

Benefits

- Compatible with previous and future generation eMMC standards for faster system integration and reduced design risk and cost

- Highly configurable and scalable IP with reduced gate count and power consumption

- Achieve unrivalled speeds up to 400MB/s

Key feature

- Compliant with eMMC Specification Version 5.1

- Supports Default speed (26Mhz), High speed (52Mhz) mode, HS200, HS400, and HS400 Enhanced mode

- Supports command queuing engine for enhanced performance

- Supports 1-bit, 4-bit, and 8-bit eMMC modes

- Supports programmable clock frequency generation to the eMMC card

- Supports Tuning for HS200 mode

- Supports Interrupt and ADMA2 transfer mode of operation

- Individual 4Kbyte data buffer for read and write

- Cyclic Redundancy Check (CRC) for command and data

- Supports timeout monitoring for a response, data, CRC token & busy

- Supports a maximum block length of 4K-byte

- Supports both single block and multi-block data transfer

- Supports auto CMD12 feature

- Supports 32-bit AXI4 memory-mapped interface towards host processor for data transfer

- Supports 32-bit AXI4 lite interface towards host processor for register access

IP validation and performance testing

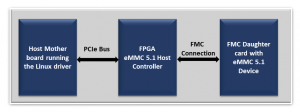

iWave provides evaluation design to validate the functionality and performance of the eMMC 5.1 Host controller. The eMMC host controller IP implemented in FPGA is inturn connected to the host motherboard via PCIe bus. To check read/write performance, iWave’s FMC Add-On-Card with eMMC device is connected through the FMC slot to the board.

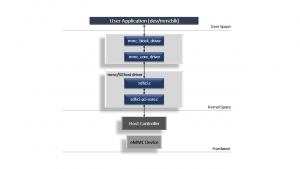

Fig 1.1: Standard application and Kernal flow

Fig 1.1: Standard application and Kernal flow

The development environment includes Linux Kernal 5.4.0. It is also supported on x86 architecture via PCIe and ARM-based platforms.

It supports a rich set of features such as general purpose partition, run time mode, bus width change, and to enable enhanced user area for the device, supports features like Erase, TRIM, Sanitize, Secure erase, secure TRIM, and RPMB. Custom APIs and generic API’s are provided as part of mmc.

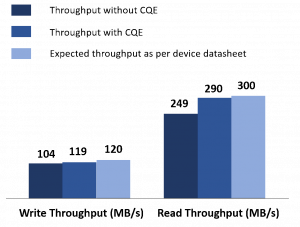

The performance chart shown below represents the write and read speeds observed with and without the use of command queuing engine (CQE).

iWave assures the user with the delivery of the IP core, warranted against defects from purchase, and dedicated technical support provided through Email, Skype, or Phone calls on a need basis. The core is available in synthesizable RTL and FPGA Netlist forms that include everything required for successful implementation, including a sophisticated testbench, simulation scripts, and synthesis scripts. IP deliverables include design document, RTL Source code, or device-specific Netlist, IP datasheet, IP integration manual, time-limited evaluation binary, and kernel driver & custom/generic API for testing of eMMC.

For more information on the IP please click here.

Keep Reading

|  |  |

| Industry compliant SATA 3.0 Host Controller IP | iWave introduces NVMe host controller IP | Mobile Security Engine using SD Memory Slave Controller |