UDP/IP Hardware Protocol Stack for High-Speed Data Transmission & Reception

iWave Presents UDP/IP Hardware Protocol Stack For High-Speed Data Transmission And Reception

A network protocol is what makes the modern internet possible. As is known, a network protocol is a set of rules that defines how data is formatted, transmitted, and received so that the computer network devices like servers, routers, and endpoints can communicate regardless of their underlying infrastructure. Without standardized protocols, the computers wouldn’t know how to engage with each other, and the internet as we know it wouldn’t exist.

With iWave’s UDP/IP Hardware protocol stack, the host processor can be offloaded from the task of UDP encapsulation and enabling media streaming with speed up to 40G even in a processor less non-SoC design, making it ideal for any standalone operation. Compared to the software stack, this core can achieve high throughput and presents high flexibility to the user by offering a configurable number of UDP transmit and receive channels. The core can be easily mapped with different programmable devices, such as Xilinx, Intel, or with any ASIC technology.

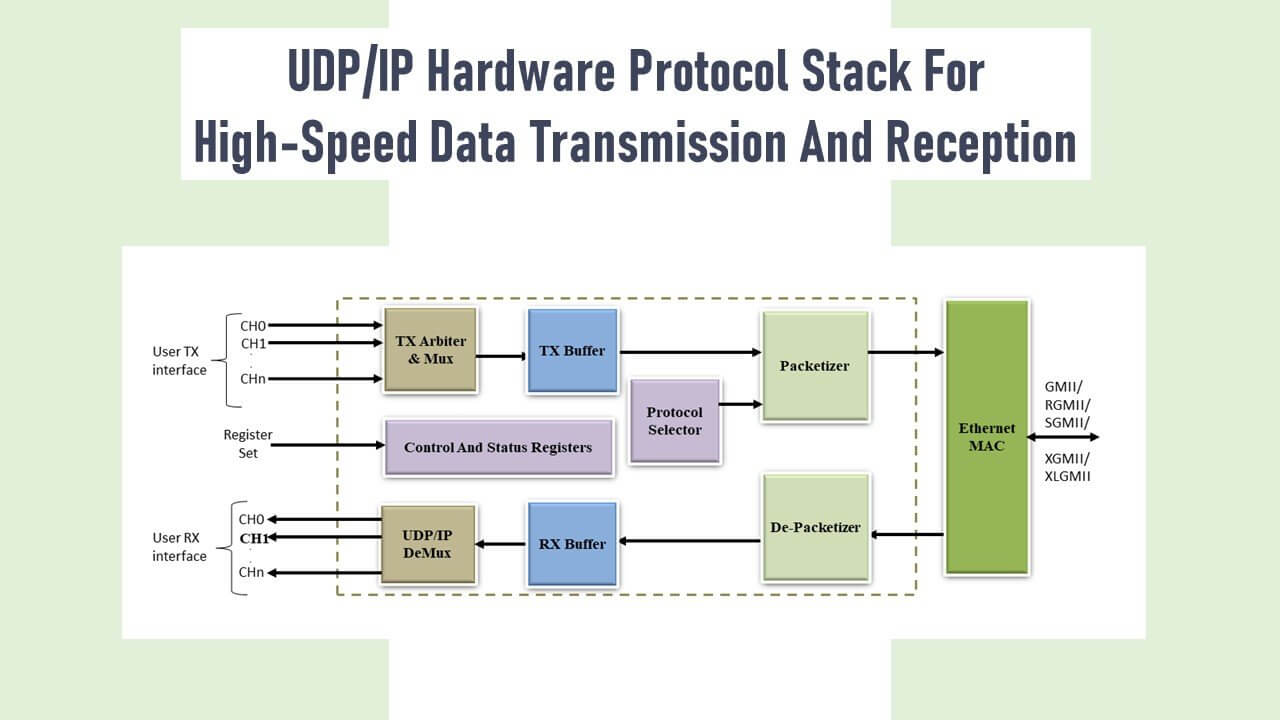

The UDP/IP Hardware Protocol stack comprises of seven modules, namely Tx Arbiter & MUX, Tx Buffer, Protocol Selector, Packetizer, De-Packetizer, Rx Buffer, and UDP/IP DeMux. The Tx Arbiter & MUX collects user data from various channels and stores them into separate FIFO’s. This module then reads these FIFO’s in a round-robin manner and sends the data to Tx Buffer that is further stored in 256bit wide FIFO. The Protocol Selector outputs a protocol number for which the packetization has to be done along with the required fields such as UDP Source and Destination ports, IP Source and Destination address, etc. The Packetizer then generates the respective frames for the DHCP, ARP, and ICMP protocols and packetizes the data from the Tx Buffer, as per UDP protocol, based on the protocol number obtained from the Protocol Selector and transmits it to the Ethernet MAC. Later, the De-Packetizer receives frames from the Ethernet MAC and removes the header fields from the frame, and stores the UDP payload data in the Rx Buffer. Then this module stores the data as well as the stream information in a FIFO. The UDP/IP DeMux module reads the data from the Rx Buffer when the entire packet is present in the FIFO and sends it to the respective user channel based on the received destination port value. Finally, the Control and Status Registers control the core functionality and report the core status.

UDP/IP Hardware protocol stack supports rich features such as

• Easy integration with 1G, 10G, and 40G Ethernet MAC

• Configurable number of UDP Transmit & Receive channels from 1 to 32

• IPV4 support without packet fragmentation

• Echo-Request & Reply messages (“ping”) of the Internet Control Message Protocol (ICMP) used to test network connectivity

• Address Resolution Protocol (ARP) for proper functioning over the internet

• UDP & IP checksum generation and validation support

• 32bit, 64bit, and 128bit AXI stream interface for transmission & reception of user data and 32bit AXI4-Lite interface for handling control and status registers

• Configurable buffer sizes for easy SoC integration

• Supports optional Dynamic Host Configuration Protocol (DHCP), client

The UDP/IP is commonly used in various time-sensitive applications, such as real-time audio-video streaming, voice over IP used by several internet-based telephonic services, online gaming, in diverse Artificial Intelligence/Machine Learning applications, internet security monitoring, to provide high-speed communication between LAN nodes, device monitoring, and control over IP networks.

iWave assures the user with the delivery of the IP core, warranted against defects from purchase, and dedicated technical support provided through Email, Skype, or Phone call on a need basis. The core is available in synthesizable RTL and FPGA Netlist forms that include everything required for successful implementation, including a sophisticated testbench, simulation scripts, and synthesis scripts.

iWave Systems brings over 20+ years of valuable experience in high-performance FPGA based design and development, offering an extensive portfolio of FPGA System On Modules, Single-board computers, and FPGA IP cores.

For more information or inquiries, please write to mktg@iwavesystems.com or contact our Regional Partners.