- Products

- Automotive

- Avionics

COTS Module

- Agilex 7 SmartNIC Card

- Zynq RFSoC ADC DAC PCIe Card

- ZU7/ZU5/ZU4 PCIe SmartNIC Card

- ZU19/17/11 PCIe SmartNIC Card

- PCIe Switch Module

- PCIe to SD 3.0 M.2 Module

- Kintex-7 PCIe Card

- Zynq ZU7/ZU5/ZU4 3U-VPX

- Virtex UltraScale+ 3U VPX

- Kintex UltraScale+ 3U VPX

- Zynq ZU19/17/11 3U VPX

- Kintex-7 3U VPX Card

- VITA 57.4 FMC+ Loopback Test Module

- VITA 57.1 FMC Loopback Test Module

- PCIe Gen4 x8 FMC Module

- PCIe Gen4 x16 FMC+ Module

- PCIe Gen3 x8 FMC Module

- Quad QSFP28 FMC+ Module

- FMC Add-On Cards

- IP Cores

- ODM Solutions

- Custom Design

- Company

Get a Quote

Please fill in the form and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Get in Touch

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

Thank you for subscribing to our newsletter!

Design Support

Software

Design Support

Software

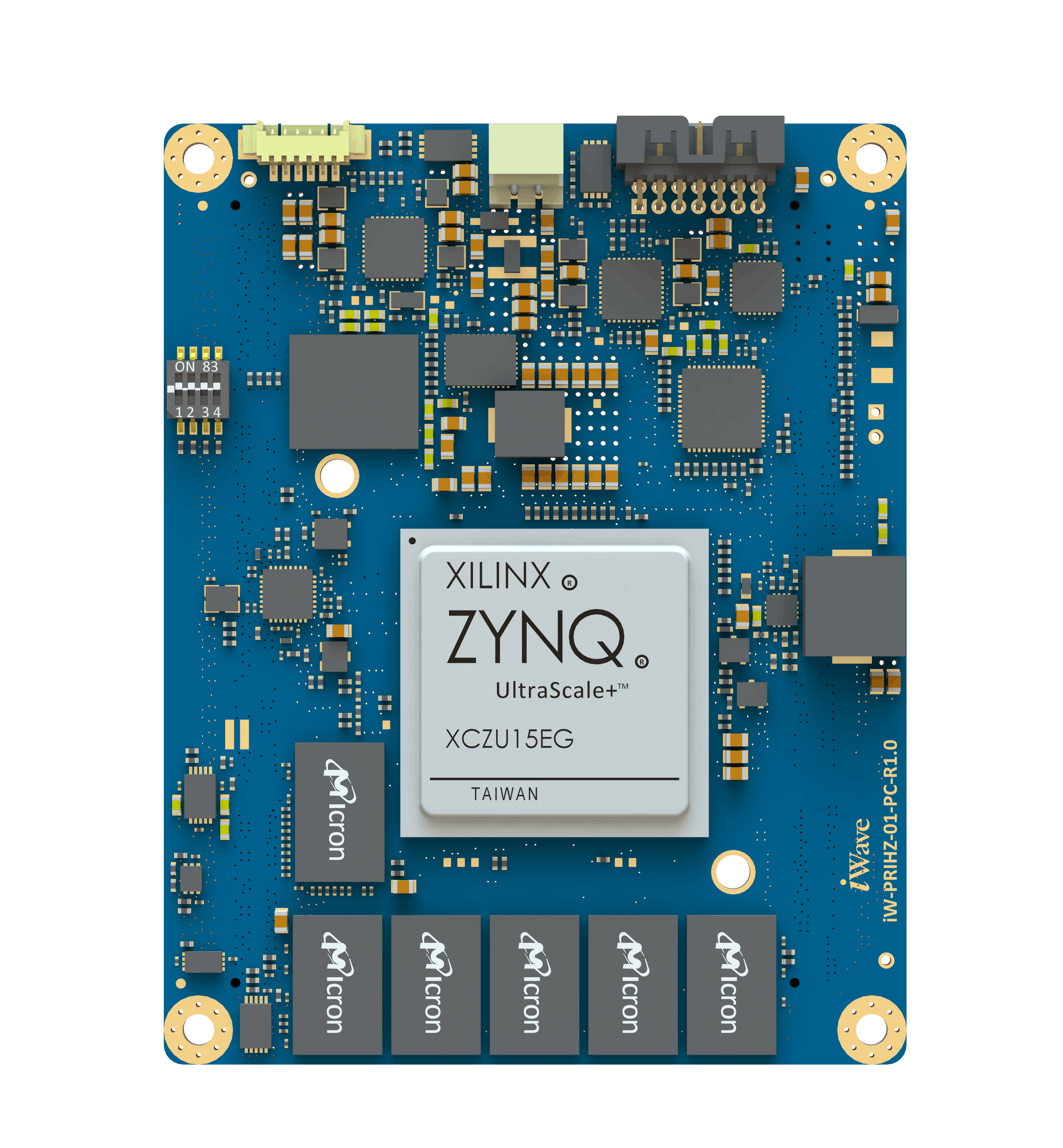

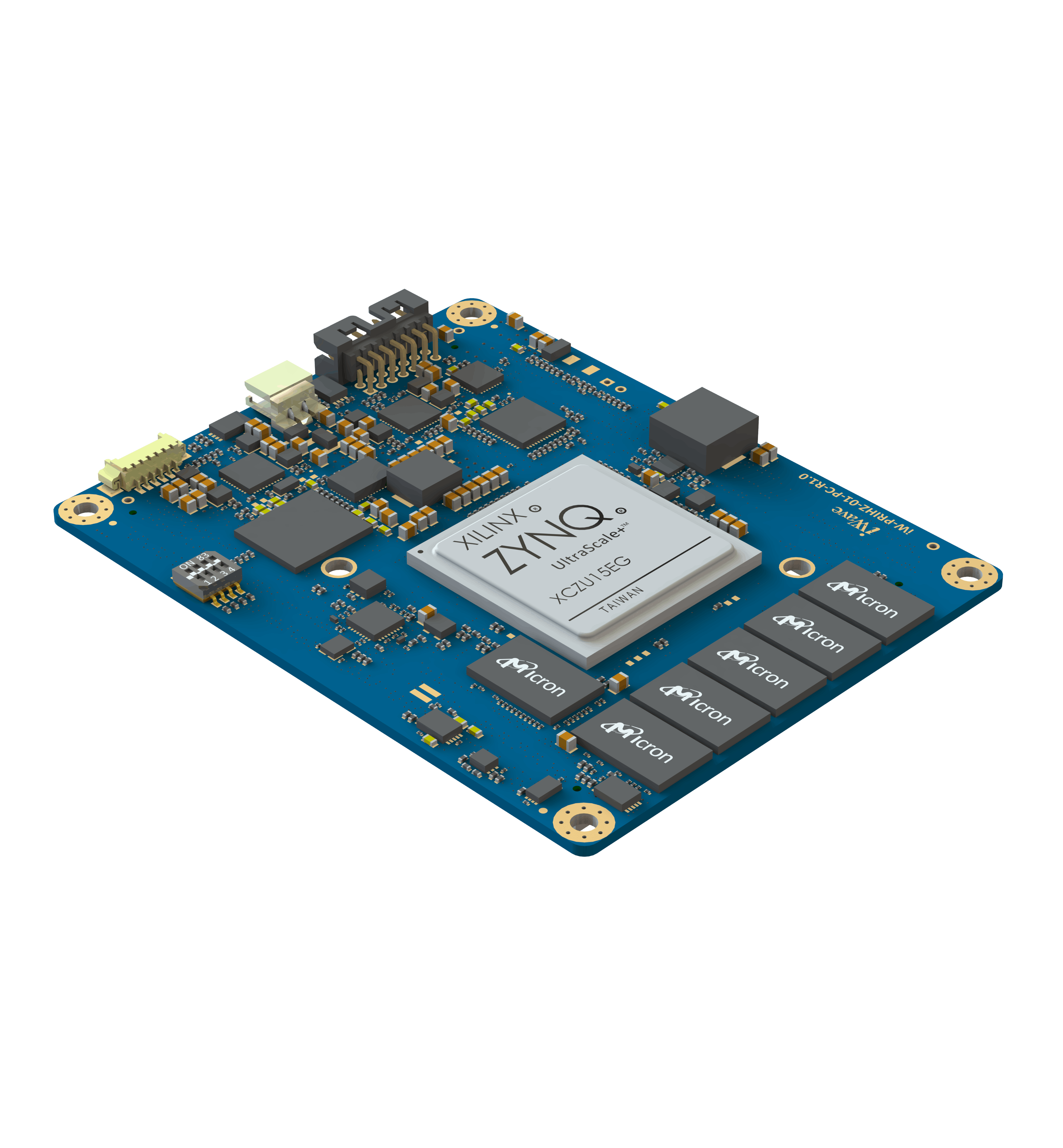

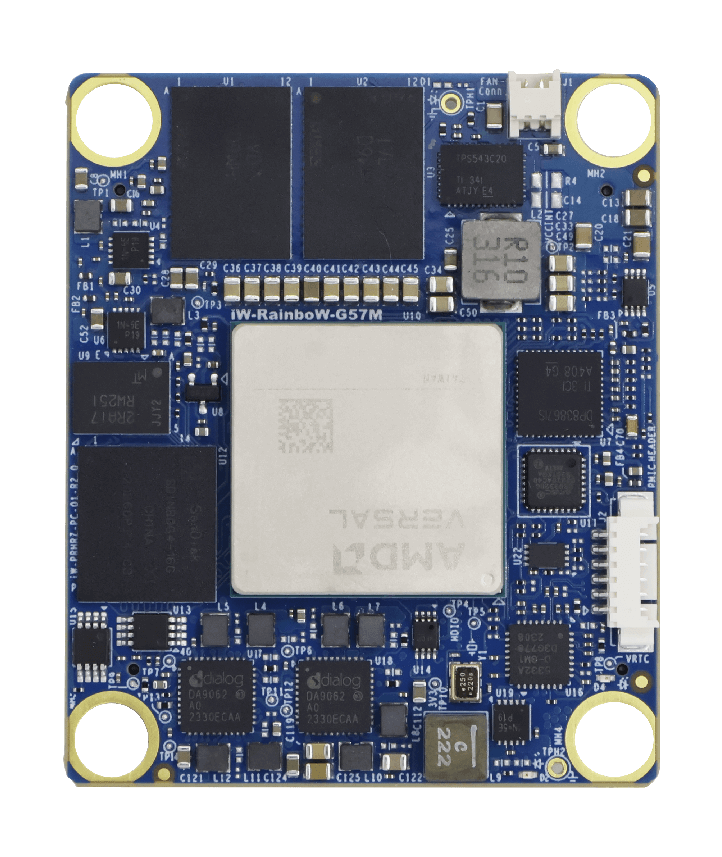

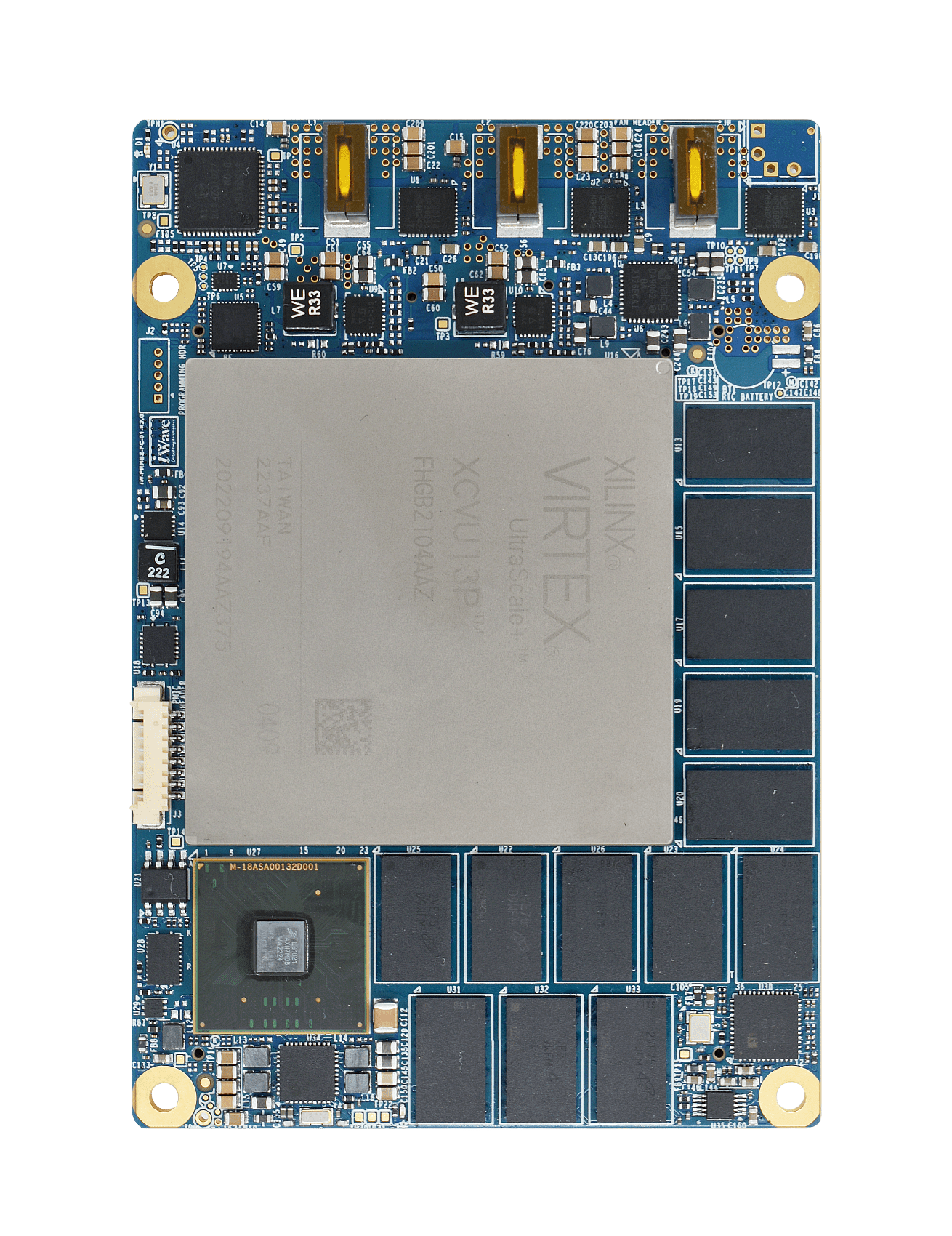

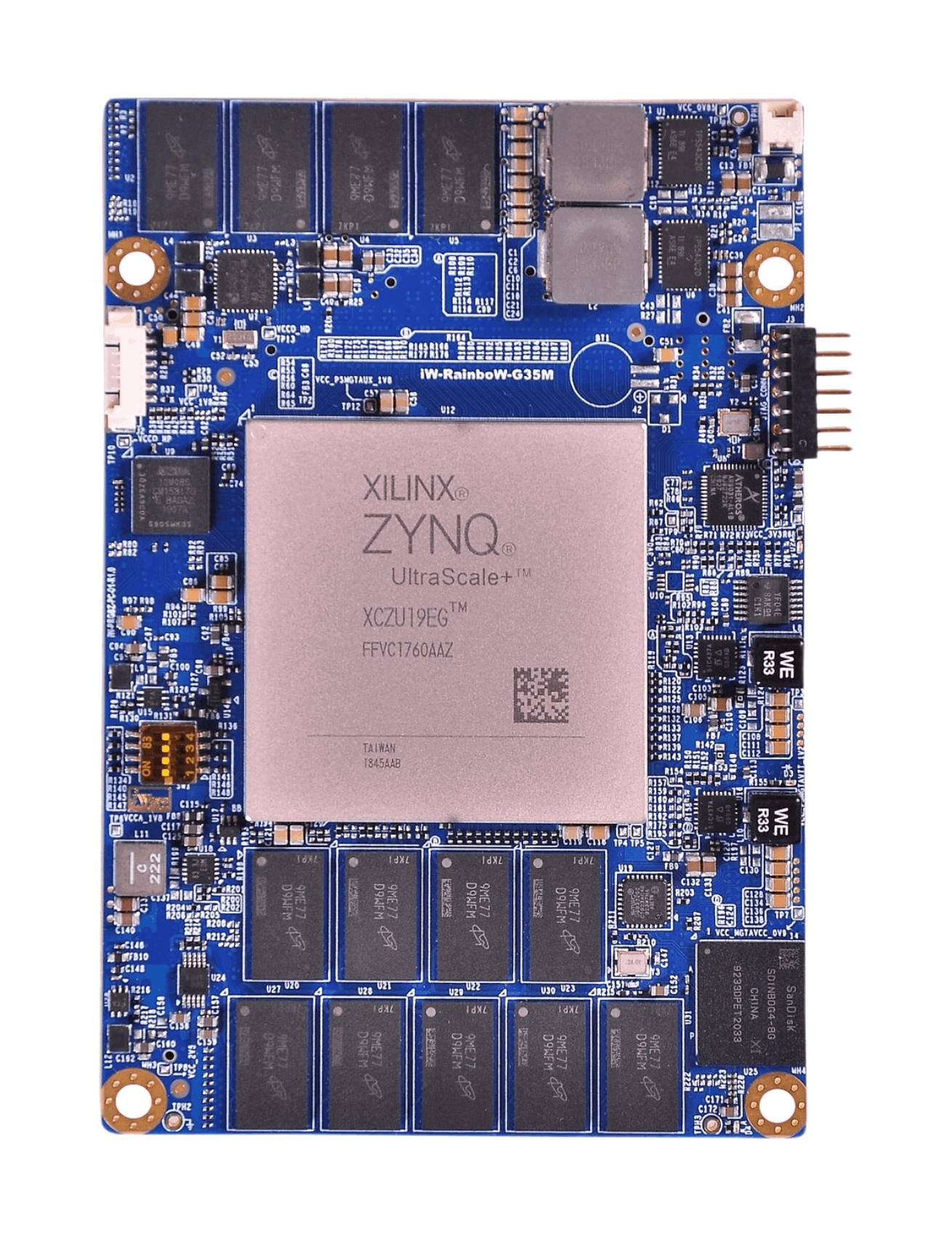

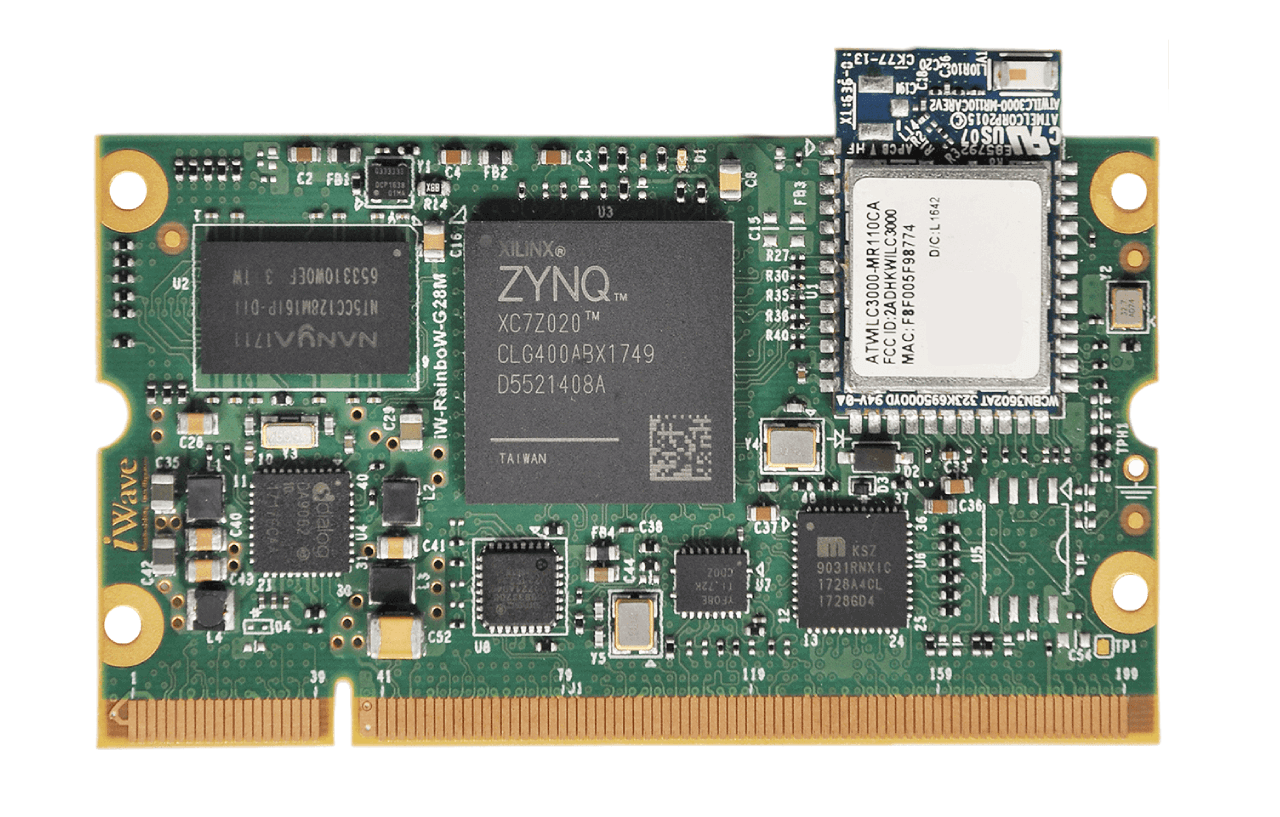

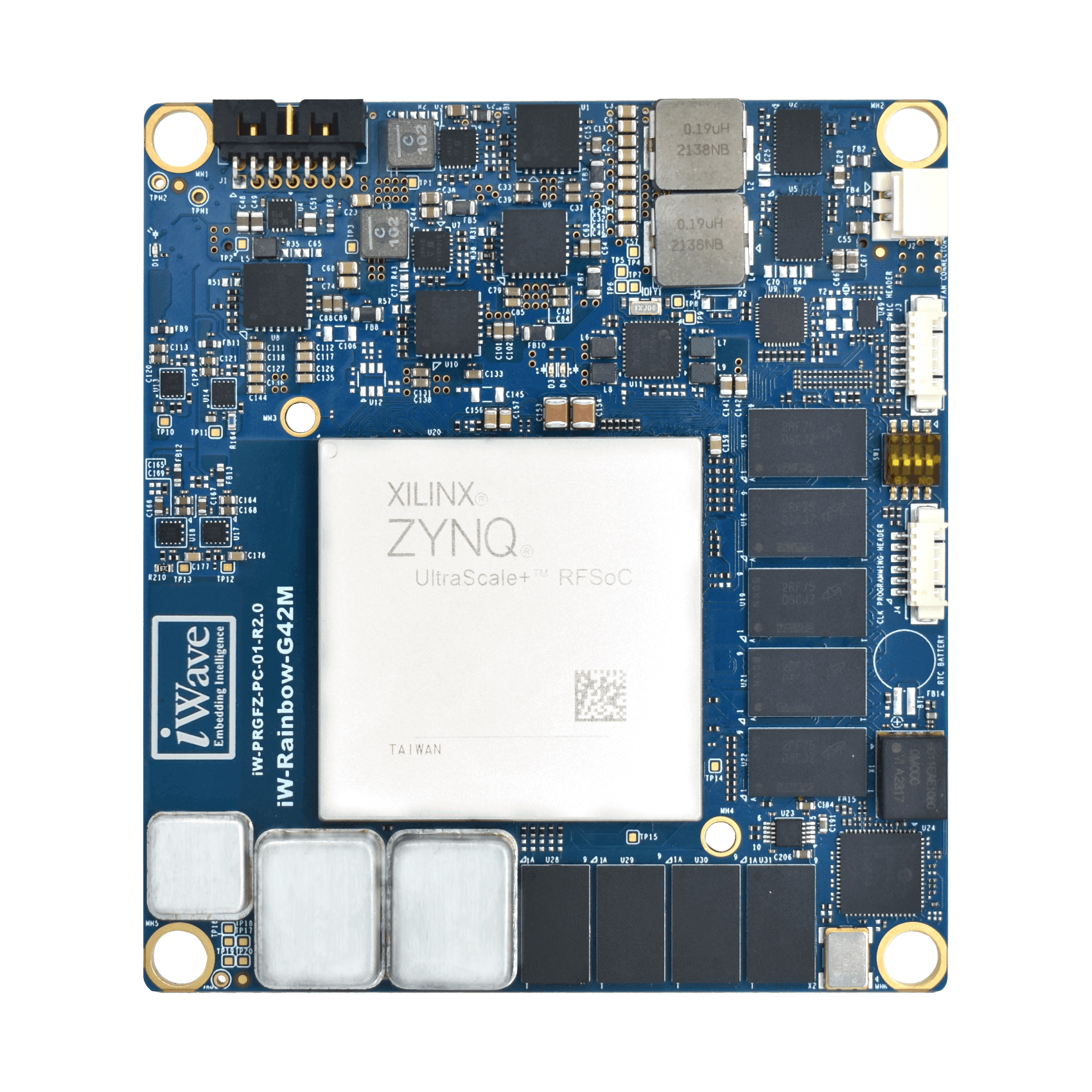

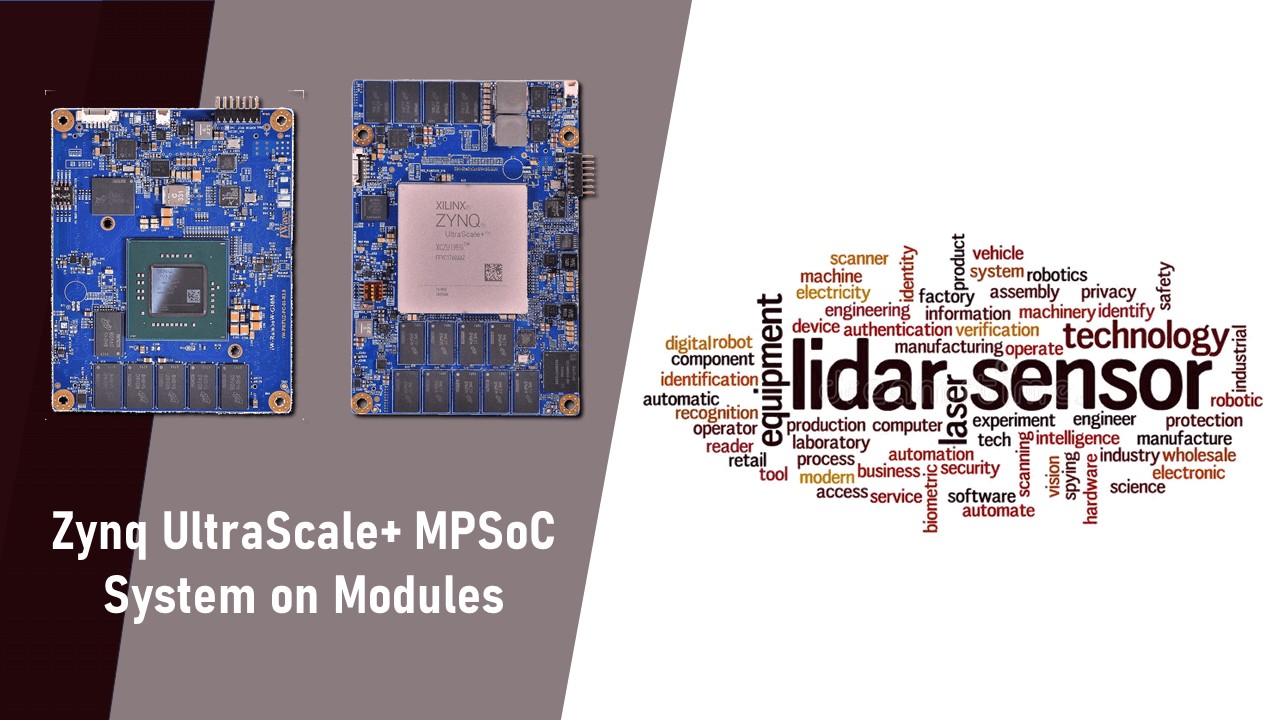

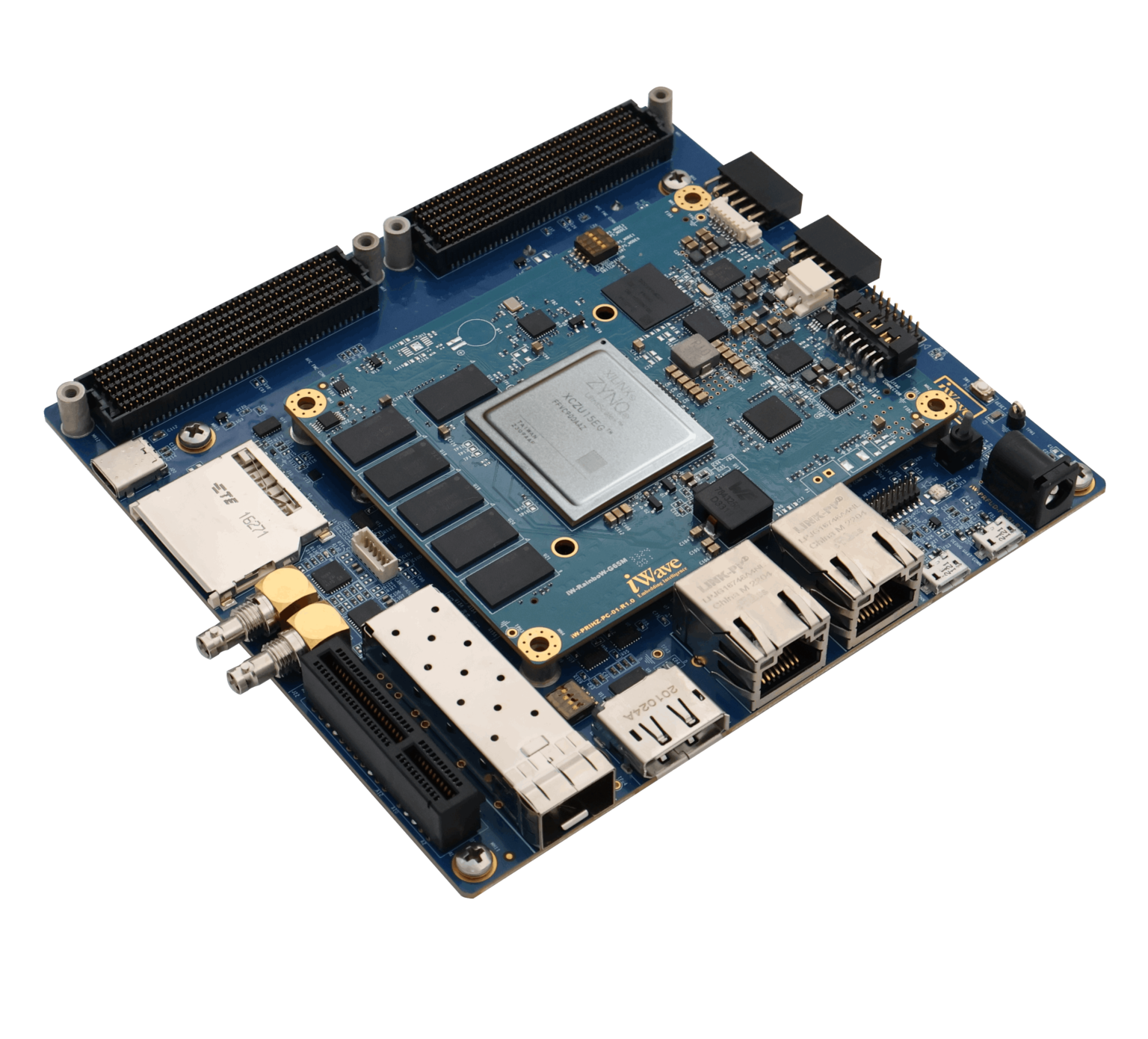

ZU15/ZU9/ZU6- Zynq UltraScale+ MPSoC System on Module

ZU15/ZU9/ZU6- Zynq UltraScale+ MPSoC System on Module

- AMD Xilinx’s ZU15/9/6 Compatible Zynq Ultrascale+ MPSoC SOM

- 64bit, 4GB PS DDR4 RAM with ECC (Upgradable)

- 16 bit, 1GB PL DDR4 RAM (Upgradable)

- 16 High-Speed Transceiver lanes (Up to 16.3Gb/s)

- 4 PS GTR Transceiver Lanes (Up to 6Gb/s)

- 8GB eMMC Flash (Upgradable)

- On-SOM Gigabit Ethernet PHY & USB2.0 transceiver

- RGMII Interface or ULPI Interface x 1

On Board Features:

| ZU15EG ZU9/6 EG/CG - Zynq Ultrascale+ MPSoC (FFVC900) | Processing System (PS/Processor)

Programming Logic (PL/FPGA)

|

|---|---|

| RAM Memory |

|

| On Board Flash |

|

| Other Interfaces |

|

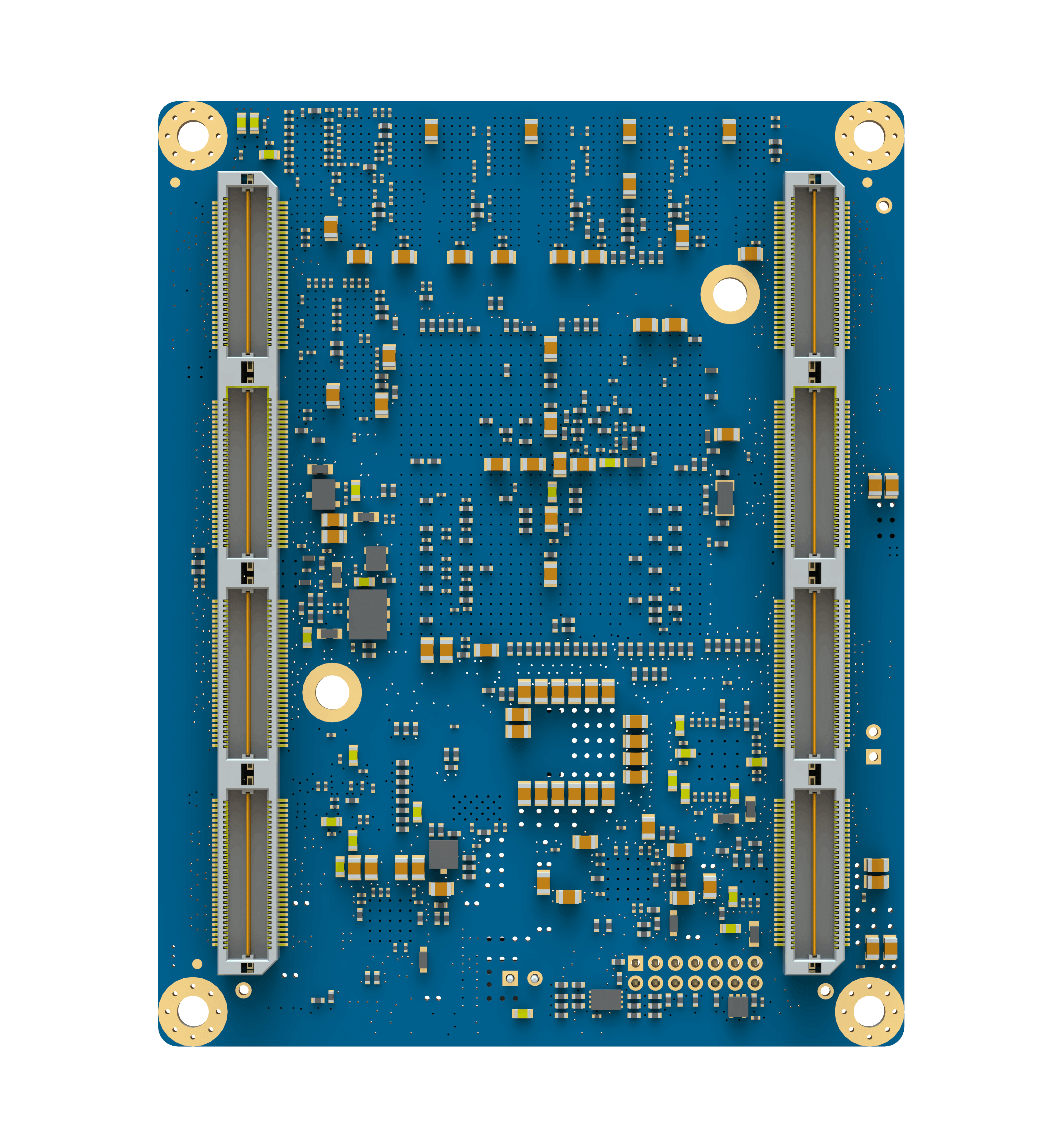

240pin High-Speed Board to Board Connector 1 Interfaces

| From PS Block |

|

|---|---|

| From PL Block |

|

240pin High-Speed Board to Board Connector 2 Interfaces

| From PS Block |

|

|---|---|

| From PL Block |

|

General Specification

| Power Supply | +5VDC +/- 5% input from Board-to-Board Connector 2 |

|---|---|

| Form Factor | 95mm X 75mm |

| Environment Specification | RoHS & REACH Compliant |

| Compliance | CE* |

Notes:

*Under Progress

DEVELOPMENT KIT

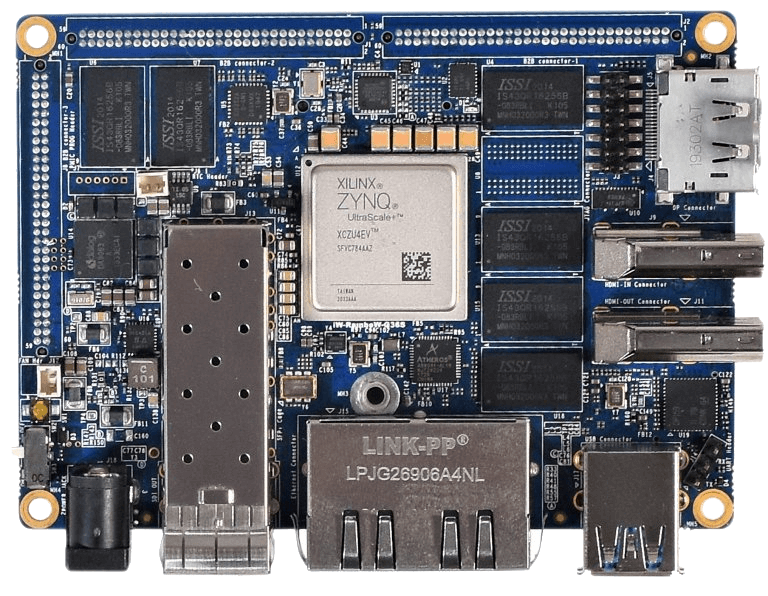

- 10G Ethernet through SFP+ Connector

- 3G SDI Video IN through HD BNC Connector

- 3G SDI Video OUT through HD BNC Connector

- Dual FMC High Pin Count (HPC) Connector

- DP1.2a Display Port Connector

- PCIe Gen2 x4 Connector

- M.2 SATA 3.1 Connector

- Dual Gigabit Ethernet through RJ45MagJack

- USB2.0 OTG through Micro-AB Connector

- USB 2.0 OTG through TypeC Connector

- USB 3.0 through TypeC connector

- Standard SD Connector

- CAN Header

- Dual PMOD Connector

- JTAG Header

- RTC Coin Cell Holder

- Operating Temperature: -20°C to +85°C

- Form Factor: 130mm x 140mm

Custom Design Sevices

iWave provides end-to-end ODM services, from concept to production, leveraging our in-house expertise in hardware design, software development, FPGA design, and mechanical enclosure design. The FPGA expertise at iWave includes RTL, high speed bus interface and transceivers, storage, video, networking, and high-speed ADC/DAC with the entire product lifecycle, from initial concept to mass production and ongoing support.

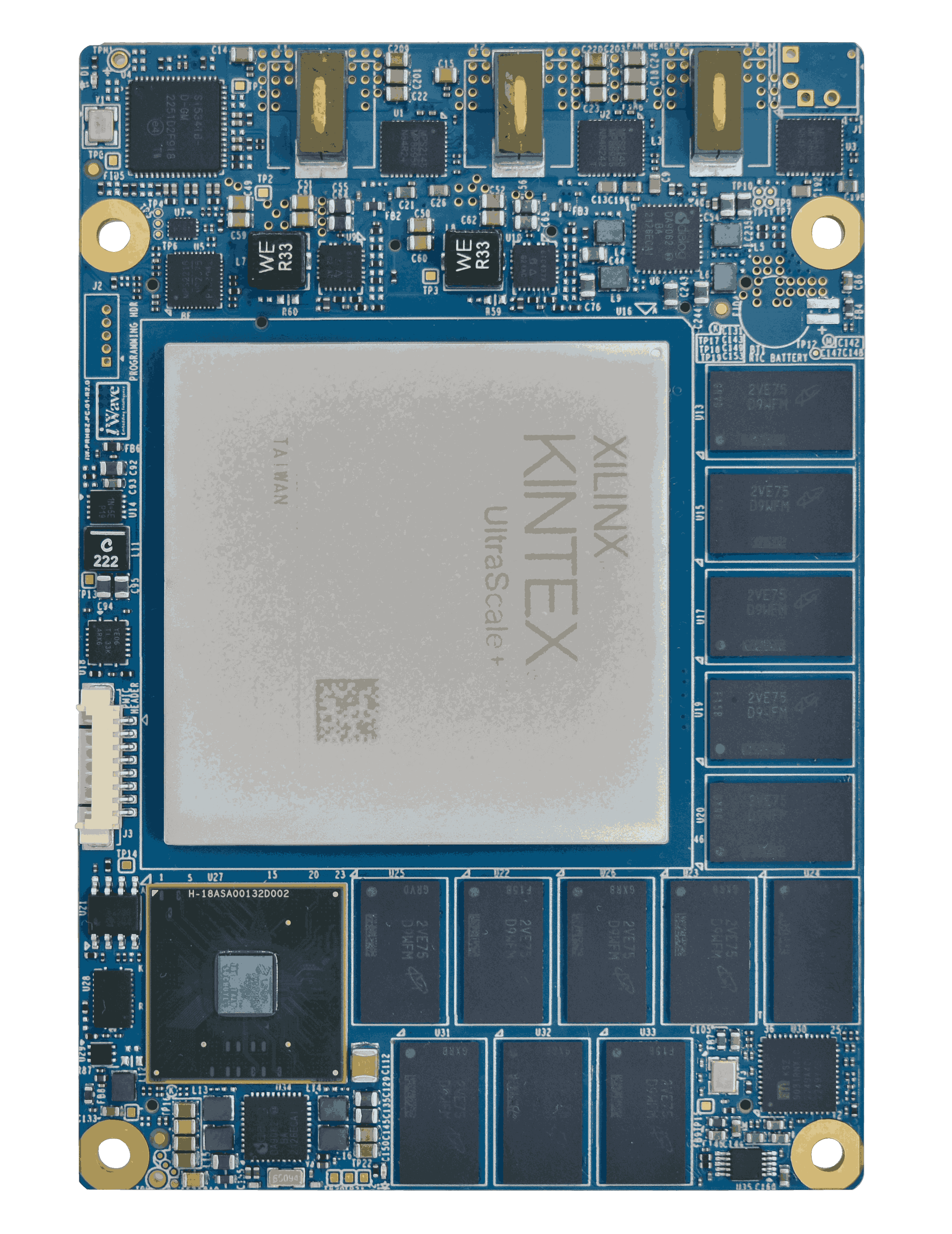

Related products

RELATED VIDEOS

Related products

Related News

Download

Please fill in the form below to download the document.

Thanks for filling in the download form.

Request Document

Please fill in the form below and we will get back to you soon!

We appreciate you contacting iWave.

Our representative will get in touch with you soon!

iWave is an embedded systems engineering and solutions company, designing solutions for the Industrial, Medical, Automotive and Avionics vertical markets, and building on our core competency of embedded expertise since 1999. Read More…

Newsletter

Copyright © 2022 iWave Systems Technologies Pvt. Ltd.