NVMe host controller: Build for high performance, efficiency & Low latency data transmission

In the last few years, the performance of storage technology has increased 100 times with the introduction of flash-based solid-state drives (SSDs), especially SSDs connected over the NVM Express interface. A protocol that is manageable and scalable for both enterprise and client computing.

So, what is NVMe?

NVM Express or NVMe (Non- Volatile Memory express) is a streamlined protocol designed to talk to solid-state drives and flash memory offering a super low latency and super high-performance framework. The interface allows the host software to communicate with non-volatile memory subsystems via a interface and is perfect for FPGA applications that require high-speed access to flash storage without an external CPU.

Benefits of NVMe for high-speed data storage

- To help deliver a high-bandwidth and low latency user experience, NVMe enables SSDs to take advantage of high-speed peripheral component interconnect express (PCIe) bus in a computer by connecting directly into it. As a result, it assists tens of thousands of parallel command queues which is much is faster compared to a hard disk drive (HDDs) and traditional flash architectures that support a single command queue.

- NVMe leverages multicore CPUs. Since it allows multiple CPU cores to share ownership of queues, arbitration, as well as priorities of queues and atomicity of commands

- Streamlined protocol optimized for register interface and command sets, to efficiently parse and manipulate data

- Delivers high throughput and faster response time for all types of enterprise workloads

Understanding I/O queues and how it works

Let’s take a look into NVMe architecture to understand how it achieves high-performance and low latency. To optimize storage and retrieval, NVMe supports multiple I/O queues up to 64K Queues each having 64K entries. On the contrary, legacy SATA and SAS can support a single queue with each having 32 and 254 entries. The NVMe host software can create a maximum number of I/O queues supported by the NVMe controller as per the system configuration and workloads.

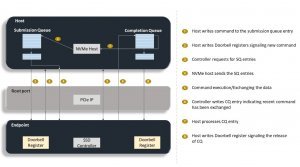

It has a paired submission and completion queue mechanism in the host memory. The Submission queue is a circular buffer with a fixed slot size where each entry is one command, similarly, the completion queue is a circular buffer with a fixed slot size where each entry is the command completion status for a specific command.

Whenever there is a new command to be executed by the NVMe controller, the NVMe host software will create a command as per the NVMe specification and will place the command inappropriate submission queue. Each Submission Queue will have its own Tail Doorbell Register to notify the presence of new command on the queue to the NVMe Controller. The controller fetches the Submission Queue data to process and execute the command. Then NVMe controller places command completion into the associated completion queue followed by an interrupt to notify the new completion status of the previously submitted command to the NVMe host software. Finally, Completion Queue data writes the Completion Queue Head Doorbell Register to notify the NVMe controller that NVMe Host Software has completed the processing of completion queue data.

Why NVMe is important for business?

With the evolution of the latest technologies like data center, mission critical, defence, AI, big data, etc. there has been a remarkable escalation in the amount of data generated, analyzed, processed, and stored, driving enterprises to opt for high-performance storage media. And NVMe is one such protocol that is built to deliver a high-performance computing environment that can efficiently eliminate the bottlenecks and scale up to meet the rising data demands. It is observed that big data and OLTP relational database platforms deployed by various organizations have to handle extensive workloads and NVMe makes real-time data-driven decisions much faster. Apart from this NVMe offers various advantages for prospects in medical, automotive, industrial, entertainment, commercial aviation, etc.

Since the FPGA-based products for NVMe allow the compute to merge with the storage at the hardware level you get higher performance, and with the processing of reconfigurable logic being directly attached to the storage, the data flows through the FPGA and is processed in real-time. It also combines high-speed data processing and control on the device which can potentially run in autonomy.

NVMe host controller by iWave Systems

The NVMe host controller by iWave is compliant with NVM Express base specification revision 1.4 that performs memory transfer to or from the NVMe storage devices like SSDs, controlled by the embedded software. It is available with flexible vendor-specific PCIe hard IP to access SSD and supports PCIe soft IP. For easy adoption in SoC implementation, the NVMe host IP comes with an AXI control and data path interface.

The NVMe host controller IP is feature-rich such as

- It supports SMART, Identify, Shutdown READ, WRITE, Flush commands

- Includes internal RAM as a data buffer without using the external DDR

- Operates with PCIe IP using PCIe interface as a physical layer for the SSD

- Uses vendor-specific PCIe root port IP

- Supports single Admin queue and single IO queues

- Supports scalable IO queues depths and Admin queue depths

- Supports NVMe devices with 512 bytes and 4096 bytes sector sizes

- Supports maximum data transfer size of 32Mb

- Supports host memory page size of 4Kbytes

- Supports AXI4-Stream interface for the data interface

- Supports AXI4-Lite interface for the control interface

iWave assures the user with the delivery of the IP core, warranted against defects from purchase, and dedicated technical support provided through Email, Skype, or Phone calls within 24 hours. The core is available in synthesizable RTL and FPGA Netlist forms that include everything required for successful implementation, including a sophisticated testbench, simulation scripts, and synthesis scripts.

More information on NVMe host controller can be found here.

For more information or inquiries, please write to mktg@iwavesystems.com or contact our Regional Partners.

Keep Reading

|  |  |

| Industry compliant SATA 3.0 Host Controller IP | ARINC 818 conversion cards for high-speed avionics video | Mobile Security Engine using SD Memory Slave Controller |